-

8/19/2019 8-PLL and Synthesizers

1/29

8 – PLL and fre uenc s nthesizers

• General structure and specification parameters of a PLL

•

• Working principle and butterfly characteristics and PLL

•

• Loop filter design criteria

• A licative exam les:

• Clock synchronization

• DSB-AM and SSB-AM coherent demodulators• FM demodulator

• Indirect, direct and hybrid frequency synthesizers

1

• Direct digital synthesizers (DDS)

-

8/19/2019 8-PLL and Synthesizers

2/29

-

8/19/2019 8-PLL and Synthesizers

3/29

General block diagram of a PLL

Phase

Detector

Loop

Filter F sVCO

VIN(AIN, ωIN, θIN)Vout=(AOUT ωOUT,θOUT)vd vc

A PLL consists of 3 basic blocks:

• A phase detector : generates an output voltage Vd whose mean value is proportionalo e p ase erence. n genera :

d= ω

IN-ω

OUT,

IN-

OUT, ω

IN+ω

OUT,

IN+

OUT

• A loop filter F(s) which extracts the low-frequency content out of Vd

• A Voltage Controlled Oscillator (VCO): generates a sine wave whose frequency is a

function of Vc

Around the free-running pulsation ωc, a 1st order approximation holdsdt

Vf cOUTω ≅=Δ

3

OUT OUT- c c c

-

8/19/2019 8-PLL and Synthesizers

4/29

Phase detectors - 1

Phase

detector

V1(ω1, θ1)

V ω θVd(ω1-ω2, ω1+ω2, θ1-θ2, θ1+θ2)

• Phase detectors are non-linear circuits to compare frequencies and

– If ω1 = ω2 Vd=f(θ1 - θ2)

– If ω1 ≠ ω2 Vd=f(ω1 - ω2 )

• Analog phase detectors are analog 4-quadrant multipliersExample: sine waves

( ) ( ) ( )[ ] ( ) ( )[ ]212121

212121

21 θ θ ω ω θ θ ω ω +++

⋅

+−+−

⋅

=⋅⋅= tVV

Kt

VV

KvvKv mmmd sinsin

( ) ( )1111 θ ω += tVtv sin ( ) ( )2222 θ ω += tVtv cos

• Using a suitable low pass-filter only the first component feeds the VCO

⋅VV

4

• ω1 = ω2, an or sma va ues o θ1 - θ2 21212

−=−≅ dmdv

-

8/19/2019 8-PLL and Synthesizers

5/29

Phase detectors - 2

• Digital phase detectors are used to calculate the phase differencesbetween two periodic binary waveforms (0 and Vmax). In this case:

τ =

where T is the period and τ is the time difference between themT

• d

Some implementations:

= dd

1) Periodic signals with 50% duty cycle: XOR logic gate

T2

θ

==

⋅Δ maxV

T

sT

s

d0 d

2

v

π Ts0 d

Kd

5

-

8/19/2019 8-PLL and Synthesizers

6/29

Phase detectors - 3

2) Impulsive waveform: S-R Flip-Flopπ 2

maxV

K d =Q

QSET

CLR

S

R

VIN

VOUT

vd

3) Periodic signals with a duty cycle different from 50%: the simplest solutionis to calculate the derivative of both signals to obtain a train of impulses

6

-

8/19/2019 8-PLL and Synthesizers

7/29

Performance parameters of a PLL

• ree-runn ng requency ωc o e• Capture range: frequency range around ωc in which a PLL is able to lock aninput signal.

– epen s on e parame ers o e er s

• Lock range: frequency range around ωc in which a PLL is able to track the

pulsation ωIN of the input signal once it is locked – epen s on y on e ga n o e er

– In general, Lock range > Capture range

Lock range =[ωc-ωlock, ωc +ωlock ]

Capture range =[ωc-ωcapture, ωc +ωcapture ]ωc-ωlock ωlockωcapture-ωcapture

• Equivalent noise bandwidth: ratio between the output power and the spectralno se ens y o an npu w e p ase no se

( )∫∞

=0

2

2

1ω ω d jHBN

7

⋅ max

-

8/19/2019 8-PLL and Synthesizers

8/29

Working principle of a PLL

• A PLL is a non-linear system. Its behaviour consists of: – a transient phase (nonlinear behaviour) capture

– - -

Open Loop Analysisssume a e oop s open e ore e

Phase Loop Vout=(AOUT ωOUT,θOUT)v vVIN(AIN, ωIN, θIN)

Detector Filter F(s)

VCO is free-running ωc=constant and ωOUT=ωc Ac

−−−−=

ωd0ωd θd Ac

8

-

8/19/2019 8-PLL and Synthesizers

9/29

Butterfly characteristic - 1

1. Assume to close the loop at a time t0 and that VIN is a input sine wave with

ω ≠ω V ≠0

2. A transient phase begins (capture) during which Vc=f (ωIN - ωc) and

ωOUT=ωc+ΔωOUT(Vc) ωOUT oscillates with an amplitude which is a function ofIN - OUT c

ωOUT tends to shift towards ωIN

3. In order to lock the input signal (i.e. ωOUT=ωIN) the frequency of input signal must

be within the capture range. Finding the capture range is difficult. A roughestimate can be obtained if we consider that when lock is reached Vc must be aconstant, i.e. ωOUT=ωIN =ωc+KcVlock and that |Vc(t0)|>|Vlock|

( )[ ]c

cINlockcINd

K

V jFKω ω

ω ω −

=>−

( )[ ]cINdccIN jFKK ω ω ω ω −

-

8/19/2019 8-PLL and Synthesizers

10/29

Butterfly characteristic - 2

4. When ωOUT =ωIN (phase lock) Vc ∝(θin-θout) whose DC component Vc ≠ 0 enablethe VCO to keep the lock (stable working point)

. ωIN c anges n me ωOUT rac s ωIN w n e oc range. ωlock s m e ythe properties of the phase comparator

Exam le: analo com arator works a roximatel in the ran e - /2 /2

( ) ( )( )OUTINdc FKtV θ θ −≅ 0 2π

θ θ ωcapture

• In the followin onl the hase lock condition will be described anal ticall

22

10

-

8/19/2019 8-PLL and Synthesizers

11/29

Butterfly characteristic - 3

• Starting from ωIN>ωc an opposite behaviourcan be observed asymmetric (butterfly Case 2: ωIN ↓

11

characteristic

-

8/19/2019 8-PLL and Synthesizers

12/29

Linear model in phase locked conditions

• After the transient ends and the PLL locks, the PLL can be modelled asa linear feedback system

Hypotheses

• =

• A linear approximation holds for all blocks of the PLL

• θIN and θOUT are assumed as the input and output signal of the PLL

Laplace domain analysis

Phase det. ( ) ( )

[ ] s s K V

OUT IN d d Θ−Θ=

Loop filter ( ) ( ) ( ) sV s F sV d c ⋅=

( ) ( ) ( ) sV K s s s ccOUT OUT =Θ=Δω

( )( ) ( ) s F K K s

s F

s

s s H

d c

d c

IN

OUT

+=

ΘΘ

=

12

-

8/19/2019 8-PLL and Synthesizers

13/29

Loop filter design criteria – 1

Kd F(s) Kc/sΘIN(s) ΘOUT(s)vd vc

+-

dcKK

• The loop filter transfer function F(s) is closely related to the the order of the PLLand it affects its performances

o oop er: = dcKKs +

|H(jω)|dB • The PLL can be modelled as a 1-st order linear system

0 dB

• PLL –3 dB bandwidth is given by KcKd

• Advantages: ωca ture≈ ωlock

• Disadvantages: spurious components due to phasecomparator nonlinearities, out-of-band noise anddouble-fre uenc terms affects VCO behaviour a

13KcKd

low-pass filter is required in any case

-

8/19/2019 8-PLL and Synthesizers

14/29

Loop filter design criteria – 2

1-order passive filter (RC cell)

dcKK1

=ω

sRCsF

+=

1 dcKKsRCs ++=

2RC

RC

Open loop pole

1ω ω dcdc

n KKRC

KK==( )

2

1

1

1

22

=++

=ξ s s RC s

s H

Resonancepulsation

2n

n

d cd c ωω K K K K

dcdc KKRCKK

1

2

11

2

1 ω

ξ ==

|H(jω)|dB • The PLL can be modelled as a 2-nd order linear s stem

0 dB ξ↑ • PLL –3 dB bandwidth is given by ~ω n

• Advanta es: o en loo –3 dB bandwidth ω can beset independently from PLL bandwidth ω n noise andspurious rejection better VCO stability

• Disadvanta es: If ω increases decreases

14

~ω n ω resonance close to ω n oscillations may occur

-

8/19/2019 8-PLL and Synthesizers

15/29

Loop filter design criteria – 3

1-order filter with a zero in the transfer function (R1R2C)

sCR1+ 21

=ω O en loo zero( )CRRs 211 ++

=12

C ( )CRR 211

1

+

=ω Open loop pole

2

( ) ( )

( ) ( ) dcdc

dc

KKKKCRsCRRs

sCRKKsH

+++

+=

2212

2 1

1=ξ 0 dB ( ) 121

ω ω dcdc

n KKCRR

KK=

+=

Resonancepulsation

( )CRR

KK

KK

CR dc

dc 21

21

2

1

+⎟⎟

⎠

⎞⎜⎜

⎝

⎛ +=ξ Damping factor

~ω n ω

Advantages: In this case we have a further degree of freedom in PLL design. In fact, bychoosin R so that we can have a maximall flat fre uenc res onse within PLL

1=ξ

15

bandwidth 2

-

8/19/2019 8-PLL and Synthesizers

16/29

A datasheet example

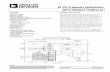

• The LM565 and LM565C are

• Contain a stable, highly- balanced phase detector withgood carrier suppression

16

-

8/19/2019 8-PLL and Synthesizers

17/29

Example: clock synchronization

PhaseExternalclock f clk

Detector

Outputc oc clk

Delayog c

circuit

• When clocking high-frequency circuits (e.g. FPGA), the clock delays betweendifferent part o the circuit can differ considerably clock skew at the output

• In this case the signal frequency is correct: only the phase has to be tuned

• Dela lock loo s DLLs are a articular kind of PLL whose ur ose is tosynchronize an input clock reference with the signals output from PADs

• A variable dela line made u of a chain of fli -flo s or variable current inverters

17

enables a fine phase tuning of the phase shift phase error depends on F(s)

-

8/19/2019 8-PLL and Synthesizers

18/29

Example: FM demodulator

BPF Phase vd(t)

vm(t)

Detector vc(t)

v t

When the PLL is lockedReceived signal

tt Atucc

θ ω += cos

=t

( ) ( ) ( ) ( )( )ttF A Atv outvcc θ θ −⋅⋅≅ 02

(1)

(2)

(5)

∞−

VCO

c

B re lacin 2 and 4 into 5 and

kc

( ) ( )[ ]tt Atv outcvout θ ω += cos

t

differentiating both members(3)

18

kc

f τ τ π

∞−= ccout v

-

8/19/2019 8-PLL and Synthesizers

19/29

Example: DSB and SSB demodulators

Low-pass

filter

Balanced

Modulator r(t)

m(t)u(t)BPF

Phase Lock c t

• PLLs can be used to recover the carrier from the input signal in the case of DSB-

• From this point of view, a PLL can be considered as a narrowband filter, whosecentral frequency tracks the carrier frequency fluctuations

( ) ( ) ( ) ( ) ( ) ( )

( )( )

( )( )2121

21

2 θ θ ω θ θ

θ ω θ ω

+++−=

=++==

ttm Atm A

tttm Atctr tu

ccc

ccc

coscos

coscos

• A low-pass filter eliminates the double frequency components

•

19

-

8/19/2019 8-PLL and Synthesizers

20/29

Frequency synthesizers• Frequency synthesizer : system that, using one or more stable frequency

references as input signals, is able to generate periodic waveforms at variable

• Frequency synthesizers are widely used in RX/TX equipment to tune the radio.

Possible techniques

• Indirect frequency synthesis: it relies on the operating principles of PLLs

• ,dividers and filters now used only in high frequency electronics

• Direct digital synthesis (DDS): it is based on a computing device and a D/A

20

converter

-

8/19/2019 8-PLL and Synthesizers

21/29

Indirect frequency synthesizers

Ref. PhaseDetector

F(s) VCOf r

f outf out/M

Programmable binary counter

Control inputs

• When the PLL is locked, it must be f r = f out /M f out = M⋅ f r

• If a programmable binary counter is used, the feedback waveform is digital with- , u

• Main problem: jitter in the period of the output waveform when M is large due to

the fact that the phase detectors operates only on f r edges between twoe ges e syn es zers s ree runn ng ecause o : – The limited stability of the VCO free-running frequency f c>> f r – The variable delay of the binary counter

21

• This scheme can be used for instance for clock multiplying

-

8/19/2019 8-PLL and Synthesizers

22/29

Improving performances - 1

Solution 1

Ref. PhaseDetector

F(s) VCO

r

f out1/M’

f out/(M’⋅ K)

binary counter

1/K

xe requencydivider= prescaler

f out/K

Control inputs

A prescaler is faster than a programmable counter and it also allows a lower jitter

• f out

= M⋅ f rwith M=M’⋅ K frequency range and resolution are the same as

• By partitioning the divider in two sections, faster components can be used

22

-

8/19/2019 8-PLL and Synthesizers

23/29

Improving performances - 2

Solution 2f r f out/N

. Detector

F(s) VCO

Programmable binary counter Control inputs

f out1/M’

f out/M1/K

Control inputs

• ,both the resolution and the range of frequencies can be greatly increased

• f out = (M ⋅ K/N)⋅ f r : the control parameters are set by software through a μP

23

-

8/19/2019 8-PLL and Synthesizers

24/29

Fractional frequency synthesizers

Ref. Phase F s VCO

f r

e ec or

Programmable binary counter

out N / N +1

s

Control

• e v er s sw c e e ween an + w a u y cyc e

⎟

⎞

⎜

⎛ −

+=

1 D D

f f out s

( ) N N f f r out

+

=

1

• The phase detector can operate at a higher frequency than in integer case

• Divider switching causes Vc and Vd voltage fluctuations compensation is

24

required

-

8/19/2019 8-PLL and Synthesizers

25/29

Direct frequency synthesizers

Ref.Harmonic

enerator

f r N⋅f r Bandpassfilter

• The signal from the oscillator is passed to a non-linear circuitarmon c generator networ , w c s es gne to pro uce a

certain amount of harmonics having a given amplitude

• n a us a e er usua y a resonan c rcu ex rac s e w s ecomponent

• With current technologies, up to n=1000 harmonics can be generated

•

• In some cases a PLL-based synthesizer can be used instead of an

25

osc a or as npu re erence s gna

-

8/19/2019 8-PLL and Synthesizers

26/29

Frequency-conversion synthesizers

Crystal

Oscillators-

…

Crystal

Oscillators-

…

1 2

Bandpass

Filter +

• This kind of synthesizers are based on heterodyne principle, i.e.:

( ) ( )[ ] ( ) ( )[ ]212121

121221

22 θ θ π θ θ π +++

⋅

+−+−

⋅

= tf f VV

tf f

VV

v out sinsin

( ) ( )1111 2 θ π += tf Vtv sin 2222 2 θ π += tf Vtv cos

• The band-pass filter removes the low-frequency beat. A high-pass filter isnot suitable because it does not filter the s urious IM com onents such

26

as (2f 1+f 2) and (2f 2+f 1)

-

8/19/2019 8-PLL and Synthesizers

27/29

Hybrid frequency synthesizers

Ref. Phase F(s) VCOf outf r

Programmable

binary counter f L

1/MLow-pass

filter (f out+ f L),(f out- f L)

out- L

• It combines frequency-conversion synthesis and indirect synthesis

on ro npu s

• f L is generated by a local oscillator. In a locked state f out= M⋅f r +f L

• e requency convers on sc eme ena es a ne un ng o out

• The frequency jitter is lower than in typical indirect PLL synthesizers

27

-

8/19/2019 8-PLL and Synthesizers

28/29

Direct digital synthesizers (DDS) - 1

Δϕ f ck

Acc+Look-up

TableDAC Low-pass

filter

• e wave orm samp es are con a ne n a oca memory as a oo -up a e

• The look-up table data are read sequentially in a circular way and converted by ahigh accuracy Digital-to-analog converter (DAC). The output filter reconstructsthe analog waveform through interpolation

• Waveform resolution depends on look-up table word width and DACs resolution

28

-

8/19/2019 8-PLL and Synthesizers

29/29

Direct Digital Synthesizers (DDS) - 2

Advantages compared with indirect frequency synthesizers

• Low phase noise (there is no any VCO)

•of the accumulator.

techniques

• Rapid switching between two waveforms with differentfrequencies: unlike PLLs there is no need for a transient phase

to lock the new frequency value

• Discrete-time signals can be modulated directly (PSK or FSK),sim l b chan in the readin order

29