Group member :- NURUL HANIM BINTI OMAR NURUL ASYEKIN BINTI KASMI NURUL HIDAYAHTUR NAZARAH ABDUL WAHAP RABIATUL ADAWIYAH BINTI IBRAHIM

Welcome message from author

This document is posted to help you gain knowledge. Please leave a comment to let me know what you think about it! Share it to your friends and learn new things together.

Transcript

Group member :-

NURUL HANIM BINTI OMAR

NURUL ASYEKIN BINTI KASMI

NURUL HIDAYAHTUR NAZARAH ABDUL WAHAP

RABIATUL ADAWIYAH BINTI IBRAHIM

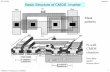

CMOS Technology depends on using both N-Type and P-Type devices on the same chip.

The two main technologies to do this task are: P-Well The substrate is N-Type. The N-Channel device

is built into a P-Type well within the parent N-Type substrate. The P-channel device is built directly on the substrate.

N-Well The substrate is P-Type. The N-channel device

is built directly on the substrate, while the P-channel device is built into a N-type well within the parent P-Type substrate.

Two more advanced technologies to do this task are:

a) Twin Tub

::Both an N-Well and a P-Well are manufactured on a lightly doped N-type substrate.

b)Silicon-on-Insulator (SOI) CMOS Process

::SOI allows the creation of independent, completely isolated nMOS and pMOS transistors virtually side-by-side on an insulating substrate.

Twin-tub process has highest overall performance compared to n-well & p-well process

This technology provides the basic for separate optimization of the nMOS and pMOS transistors.

For starting material is an n+ or p+ substrate, with a lightly doped epitaxial layer on top.

This epitaxial layer provides the actual substrate on which the n-well and the p-well are formed.

Fabrication involves the implementation of semiconductor processes to build a MOSFET transistor and compatible passive components as an integrated circuit.

MASK 1 – OXIDATION

MASK 2 - PATTERN TO EXPOSE NMOS AND PMOS REGION

MASK 3 - PATTERN POLY ON THE GATE OXIDE

MASK 4 - IMPLANTATION OF P-TYPE

MASK 5 - IMPLANTATION OF N - TYPE

MASK 6 - OXIDE PATTERN FOR CONTACT HOLE

MASK 7 - DEPOSIT METAL AND PATTERN

MASK 8 - PASSIVATION OXIDE AND PATTERN BONDING PADS

8 MASK INVOLVE IN P-WELL FABRICATION PROCESS

15 MASK INVOLVE IN N-WELL FABRICATION

PROCESS

MASK 1 – Grow a thin silicon dioxide region

on a wafer.

MASK 2 - Photoresist is removed and high-

temperature oxidation is performed.

MASK 3 - A global n-type field (channel

stop) implanted is performed.

MASK 4 - A global p-type field (channel stop)

implanted is performed.

MASK 5 - Growth the thick silicon dioxide layer over the entire wafer.

MASK 6 - Growth of the gate thin oxide and deposition of Polysilicon.

MASK 7 - Removal of polysilicon and formation of the sidewall spacers.

MASK 8 - Implantation of NMOS source and drain and contact to n-well.

MASK 9 – Remove sidewall spacers and implant the NMOS lightly doped source/drains.

MASK10 - Implant the PMOS source/drains and contacts to the p- substrate.

MASK 11 - Anneal to activate the implanted ions.

MASK 12 - Deposit a thick oxide layer (BPSG - borophosphosilicate glass).

MASK 13 - Open contacts, deposit first level metal and etch unwanted metal.

MASK 14 - Deposit another interlayer dielectric (CVD SiO2), open contacts, deposit second level metal.

MASK 15 –Etch unwanted metal and deposit a passivation layer and open over bonding pads.

Advantages Disadvantages

- Kebolehan tinggi kerana kadar

kapasitan berparasit rendah.

Proses penyediaan rumit

kerana memerlukan pembinaan

dua telaga berasingan

Related Documents