S. Ventura a *, D. Ferrusca a , M. Velázquez a , E. Ibarra-Medel a and V. Gómez-Rivera a . a Instituto Nacional de Astrofísica, Óptica y Electrónica, Luis Enrique Erro No. 1, Tonantzintla, Puebla, México We present the hardware and software process to implement an algorithm on a Kintex-7 FPGA board for multiplexing and de multiplexing bias signals for superconducting mm-wavelength detector arrays operating at sub-Kelvin temperatures. The process of programming the board using MATLAB and Vivado of Xilinx is explained. In order to test the performance of this method, an 8-channel resonator circuit at 4 K is fed with a multi-tone signal (0.3-1 MHz) and measured by a SQUID in a TES-scheme read out . The algorithm and set-up for preliminary tests and debugging are presented as well as some current results. Conclusions and Future work. We are using Simulink and Vivado for programming a FPGA board for a FDM scheme with good results so far. The inherent complexity of FPGA projects usually implies the participation of a experienced team in digital systems. Nevertheless, the labor of programming could be greatly simplified by using tools for planning and testing each stage of the work before make the actual code in VHDL. This also could save time in the whole process but specially during debugging the code. The next step in our project is to finish tests using the SQUID and the resonator circuit before continue with the design of an integrated circuit with real detectors. Millimeter Wave Instrumentation Laboratory Kintex-7 FPGA board for multiplexing and demultiplexing signals in a FDM readout for superconducting mm-wavelength detectors Fig. 1. Block diagram of the FDM scheme and the main components of the system: Xilinx Kintex-7 FPGA DSP Development Kit with High-Speed Analog, which includes: FPGA, FMC-150 mezzanine card. The SQUID, resonant circuit and computer are also showed. Progress References. Gao, J., Griffin, D., Hartog, R. D., Kiviranta, M., Lange, G. D., Leeuwen, B. V., Macculi, C., Ravera, L., Trappe, N., Weers, H. V., and Withington, S. , 2–5 (2011). Hartog, R. D., Audley, M. D., Beyer, J., Bruijn, M. P., Korte, P. D., Gottardi, L., Hijmering, R., Jackson, B., Nieuwenhuizen, A., Kuur, J. V. D., Leeuwen, B.-j. V., and Loon, D. V. 8452, 3–11 (2012). Hattori, K., Arnold, K., Barron, D., Dobbs, M., De Haan, T., Harrington, N., Hasegawa, M., Hazumi, M., Holzapfel, W. L., Keating, B., Lee, A. T., Morii, H., Myers, M. J., Smecher, G., Suzuki, A., and Tomaru, T. Nuclear Instruments and Methods in Physics Research, Section A: Accelerators, Spectrometers, Detectors and Associated Equipment 732, 299–302 (2013). Kenyon, M., Beyer, a. D., Bumble, B., Echternach, P. M., Holmes, W. a., and Bradford, C. M. Journal of Low Temperature Physics 176(3-4), 376–382 (2014). Kimura, S., Masui, K., Takei, Y., Mitsuda, K., Yamasaki, N. Y., Fujimoto, R., Morooka, T., and Nakayama, S. Journal of Low Temperature Physics 151(3-4 PART 2), 946–951 (2008). Lanting, T. M., Arnold, K., Cho, H. M., Clarke, J., Dobbs, M., Holzapfel, W., Lee, A. T., Lueker, M., Richards, P. L., Smith, a. D., and Spieler, H. G. Nuclear Instruments and Methods in Physics Research, Section A: Accelerators, Spectrometers, Detectors and Associated Equipment 559, 793–795 (2006). Mehl, J., Ade, P. a. R., Basu, K., Becker, D., Bender, a., Bertoldi, F., Cho, H. M., Dobbs, M., Halverson, N. W., Holzapfel, W. L., Gusten, R., Kennedy, J., Kneissl, R., Kreysa, E., Lanting, T. M., Lee, a. T., Lueker, M., Menten, K. M., Muders, D., Nord, M., Pacaud, F., Plagge, T., Richards, P. L., Schilke, P., Schwan, D., Spieler, H., Weiss, a., and White, M. Journal of Low Temperature Physics 151, 697–702 (2008). Vaccarone, R., Strata, F., Gatti, F., Gallinaro, G., Ribeiro Gomes, M., Ferrari, L., and Parodi, L. Journal of Low Temperature Physics 151(3-4 PART 2), 921–926 (2008). Vaccarone, R. Journal of Low Temperature Physics 151(3-4 PART 2), 915–920 (2008). Yamamoto, R., Sakai, K., Takei, Y., Yamasaki, N. Y., and Mitsuda, K. Journal of Low Temperature Physics 176(3-4), 453–458 (2014). FPGA Design and Co-design. http://www.mathworks.com/solutions/fpga-design/simulink-with-xilinx-system-generator-for-dsp.html Vivado Design Suite. http://www.xilinx.com/products/design-tools/vivado.html * [email protected], [email protected] Computer Block diagram of the signals FPGA Kintex-7 card FMC-150 Card Resonant circuit sensors Signals Generator based on a DDS compiler Bias signal 16 bits 245MHz SQUID Noise: 3.13μφ/√Hz Control Nuller Demodulation 4K Modulated signal 14 bits 245MHz DAC DAC3283 Dual channel 800 MSPS ADC ADS6249 250MSPS Fig. 8. Generated carriers and negative signal with 16 bits of resolution are looped back from the DAC (14 bits) to the ADC for testing and debugging the VHDL code. Fig. 9. Spectrum of the carrier signals according to the actual frequencies of the resonator circuit (see figure 4). We develop a code for communicating the FPGA with the ADC and DAC. We are also capable to generate bias signal and its nuller at frequencies that corresponds to channels in the resonator circuit. Code for de-multiplexing is under development. The SQUID and the resonator are installed at the cryostat and tests are being performed. Fig. 10. The number of channels is easily reconfigurable by software, limited by the system clock as well as DAC and ADC specs.

Welcome message from author

This document is posted to help you gain knowledge. Please leave a comment to let me know what you think about it! Share it to your friends and learn new things together.

Transcript

To ADC

From DAC

Detectors

S. Venturaa*, D. Ferruscaa, M. Velázqueza, E. Ibarra-Medela and V. Gómez-Riveraa.

aInstituto Nacional de Astrofísica, Óptica y Electrónica, Luis Enrique Erro No. 1, Tonantzintla, Puebla, México

We present the hardware and software process to implement an algorithm on a Kintex-7 FPGA board for multiplexing and de multiplexing bias signals for superconducting mm-wavelength detector arrays operating at sub-Kelvin

temperatures. The process of programming the board using MATLAB and Vivado of Xilinx is explained. In order to test the performance of this method, an 8-channel resonator circuit at 4 K is fed with a multi-tone signal (0.3-1 MHz) and

measured by a SQUID in a TES-scheme read out . The algorithm and set-up for preliminary tests and debugging are presented as well as some current results.

Conclusions and Future work.

We are using Simulink and Vivado for programming a FPGA board for a FDM scheme with good results so far. The inherent complexity of FPGA projects usually implies the

participation of a experienced team in digital systems. Nevertheless, the labor of programming could be greatly simplified by using tools for planning and testing each stage of the work

before make the actual code in VHDL. This also could save time in the whole process but specially during debugging the code. The next step in our project is to finish tests using the

SQUID and the resonator circuit before continue with the design of an integrated circuit with real detectors.

Experimental hardware

Millimeter Wave Instrumentation Laboratory

Kintex-7 FPGA board for multiplexing and demultiplexing signals in a FDM readout for superconducting mm-wavelength detectors

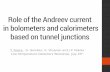

Vivado and Matlab programming

Fig. 1. Block diagram of the FDM scheme and the main components of the system: Xilinx Kintex-7 FPGA DSP Development Kit with High-Speed Analog, which includes: FPGA, FMC-150 mezzanine card. The SQUID, resonant circuit and computer are also showed.

Progress

Design and co-simulation of signal generation and

demodulation. Matlab + Simulink + System

Generator + HDL Coder

Programming FPGA. Vivado : IO pin assigment,

Synthesis, .bit files, etc.

Fig. 3. Cold plate at 4K, Quantum Design SQUID and resonant circuit,

Fig. 2. Xilinx Kintex-7 FPGA DSP Development Kit with High-Speed Analog.

Xilinx KC705 Development Board - 326,080 Logic Cells - Oscillator up to 810 MHz 4DSP FMC150 High-Speed ADC/DAC FMC Module - Dual 14-bit, 250 MSPS

(ADC) - Dual 16-bit, 800 MSPS

(DAC) .

Fig. 4. Resonant circuit for test. Design (a) and circuit using dummy sensors (b) for first test. The integrated circuit is under development.

References. Gao, J., Griffin, D., Hartog, R. D., Kiviranta, M., Lange, G. D., Leeuwen, B. V., Macculi, C., Ravera, L., Trappe, N., Weers, H. V., and Withington, S. , 2–5 (2011). Hartog, R. D., Audley, M. D., Beyer, J., Bruijn, M. P., Korte, P. D., Gottardi, L., Hijmering, R., Jackson, B., Nieuwenhuizen, A., Kuur, J. V. D., Leeuwen, B.-j. V., and Loon, D. V. 8452, 3–11 (2012). Hattori, K., Arnold, K., Barron, D., Dobbs, M., De Haan, T., Harrington, N., Hasegawa, M., Hazumi, M., Holzapfel, W. L., Keating, B., Lee, A. T., Morii, H., Myers, M. J., Smecher, G., Suzuki, A., and Tomaru, T. Nuclear Instruments and Methods in Physics Research, Section A: Accelerators, Spectrometers, Detectors and Associated Equipment 732, 299–302 (2013). Kenyon, M., Beyer, a. D., Bumble, B., Echternach, P. M., Holmes, W. a., and Bradford, C. M. Journal of Low Temperature Physics 176(3-4), 376–382 (2014). Kimura, S., Masui, K., Takei, Y., Mitsuda, K., Yamasaki, N. Y., Fujimoto, R., Morooka, T., and Nakayama, S. Journal of Low Temperature Physics 151(3-4 PART 2), 946–951 (2008). Lanting, T. M., Arnold, K., Cho, H. M., Clarke, J., Dobbs, M., Holzapfel, W., Lee, A. T., Lueker, M., Richards, P. L., Smith, a. D., and Spieler, H. G. Nuclear Instruments and Methods in Physics Research, Section A: Accelerators, Spectrometers, Detectors and Associated Equipment 559, 793–795 (2006). Mehl, J., Ade, P. a. R., Basu, K., Becker, D., Bender, a., Bertoldi, F., Cho, H. M., Dobbs, M., Halverson, N. W., Holzapfel, W. L., Gusten, R., Kennedy, J., Kneissl, R., Kreysa, E., Lanting, T. M., Lee, a. T., Lueker, M., Menten, K. M., Muders, D., Nord, M., Pacaud, F., Plagge, T., Richards, P. L., Schilke, P., Schwan, D., Spieler, H., Weiss, a., and White, M. Journal of Low Temperature Physics 151, 697–702 (2008). Vaccarone, R., Strata, F., Gatti, F., Gallinaro, G., Ribeiro Gomes, M., Ferrari, L., and Parodi, L. Journal of Low Temperature Physics 151(3-4 PART 2), 921–926 (2008). Vaccarone, R. Journal of Low Temperature Physics 151(3-4 PART 2), 915–920 (2008). Yamamoto, R., Sakai, K., Takei, Y., Yamasaki, N. Y., and Mitsuda, K. Journal of Low Temperature Physics 176(3-4), 453–458 (2014). FPGA Design and Co-design. http://www.mathworks.com/solutions/fpga-design/simulink-with-xilinx-system-generator-for-dsp.html Vivado Design Suite. http://www.xilinx.com/products/design-tools/vivado.html

a)

b)

DDS

FMC150 Card

SPI control

Demodulation

ABS LPF

ABS LPF

ABS LPF

Channel 1

Channel 2

Channel n

To PC

BPF

BPF

BPF

Clock (245MHz)

DAC3283 800 MSPS

ADS6249 250MSPS

Bias signal

Nuller

Modulated signal

Bias signal 16 bits

Modulated signal 14 bits

Fig. 7. Block diagram of the algorithm used for programming the FPGA and controlling the FMC150 card. The block diagram includes generation and demodulation of the signals.

Fig. 6. Testing different algorithms is faster using Simulink instead of programming directly in VHDL compilers. Code can be generated from Simulink (MATLAB 2015) models also, although some extra work was done in Vivado 2012 from Xilinx in order to program in a proper way the FPGA.

* [email protected], [email protected]

Computer

Block diagram of the signals

FPGA Kintex-7 card

FMC-150 Card

Resonant circuit

sensors

Signals Generator

based on a DDS compiler

Bias signal 16 bits

245MHz

SQUID Noise:

3.13µφ/√Hz

Control

Nuller

Demodulation

4K

Modulated signal 14 bits

245MHz

DAC DAC3283

Dual channel 800 MSPS

ADC ADS6249

250MSPS

Fig. 5. Section view of the cryostat used for tests, showing the cold plates, radiation shields and windows. Cooling capacity: [email protected].

Fig. 8. Generated carriers and negative signal with 16 bits of resolution are looped back from the DAC (14 bits) to the ADC for testing and debugging the VHDL code.

Fig. 9. Spectrum of the carrier signals according to the actual frequencies of the resonator circuit (see figure 4).

We develop a code for communicating the FPGA with the ADC and DAC. We are also capable to generate bias signal and its nuller at frequencies that corresponds to channels in the resonator circuit. Code for de-multiplexing is under development. The SQUID and the resonator are installed at the cryostat and tests are being performed.

Fig. 10. The number of channels is easily reconfigurable by software, limited by the system clock as well as DAC and ADC specs.

Main modules in VHDL code

Related Documents