Short Course On Phase-Locked Loops IEEE Circuit and System Society, San Diego, CA Analog Frequency Synthesizers Michael H. Perrott September 16, 2009 Copyright © 2009 by Michael H. Perrott All rights reserved.

Welcome message from author

This document is posted to help you gain knowledge. Please leave a comment to let me know what you think about it! Share it to your friends and learn new things together.

Transcript

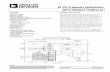

Short Course On Phase-Locked LoopsIEEE Circuit and System Society, San Diego, CA

Analog Frequency Synthesizers

Michael H. PerrottSeptember 16, 2009

Copyright © 2009 by Michael H. PerrottAll rights reserved.

2M.H. Perrott

What is a Phase-Locked Loop (PLL)?

e(t) v(t) out(t)ref(t) Analog

Loop FilterPhase

Detect

VCO

ref(t)

out(t)

e(t) v(t)

ref(t)

out(t)

e(t) v(t)

de BellescizeOnde Electr, 1932

VCO efficiently provides oscillating waveform with variable frequencyPLL synchronizes VCO frequency to input reference frequency through feedback- Key block is phase detector

Realized as digital gates that create pulsed signals

3M.H. Perrott

Integer-N Frequency Synthesizers

Use digital counter structure to divide VCO frequency- Constraint: must divide by integer values

Use PLL to synchronize reference and divider output

e(t) v(t) out(t)ref(t) Analog

Loop FilterPhase

Detect

VCO

ref(t)

div(t)

e(t) v(t)

Divider

N

Fout = N Fref

div(t) Sepe and JohnstonUS Patent (1968)

Output frequency is digitally controlled

4M.H. Perrott

Integer-N Frequency Synthesizers in Wireless Systems

Design Issues: low noise, fast settling time, low power

Zin

Zo LNA To Filter

From Antennaand Bandpass

Filter

PC boardtrace

PackageInterface

LO signal

MixerRF in IF out

FrequencySynthesizer

ReferenceFrequency

VCO

PFD ChargePump

out(t)e(t) v(t)

N

LoopFilter

DividerVCO

ref(t)

div(t)

v(t) out(t)ref(t)

5M.H. Perrott

Fractional-N Frequency Synthesizers

Dither divide value to achieve fractional divide values- PLL loop filter smooths the resulting variations

Very high frequency resolution is achieved

e(t) v(t) out(t)ref(t) Analog

Loop FilterPhase

Detect

VCO

Divider

N[k]

Fout = M.F Fref

div(t)

Nsd[k] Σ−Δ

ModulatorM.F

ref(t)

div(t)

e(t) v(t)

6M.H. Perrott

Going Digital …

Digital loop filter: compact area, insensitive to leakageChallenges: - Time-to-Digital Converter (TDC)- Digitally-Controlled Oscillator (DCO)

Staszewski et. al.,TCAS II, Nov 2003

out(t)ref(t) Analog

Loop FilterPhase

Detect

VCO

Time

-to-

Digital

out(t)ref(t) Digital

Loop Filter

DCO

Divider

Divider

7M.H. Perrott

Outline of PLL Short Course

Analog frequency synthesizers- Integer-N synthesizers and PLL background- Fractional-N synthesizers

Digital frequency synthesizers- Modeling and noise analysis- Time-to-digital conversion

8M.H. Perrott

Outline of Integer-N Frequency Synthesizer Talk

PFDout(t)e(t) v(t)

N

LoopFilter

DividerVCO

ref(t)

div(t)

Fout = N FrefFref

Overview of PLL BlocksSystem Level Modeling- Transfer function analysis- Nonlinear behavior- Type I versus Type II systems

Noise Analysis

9M.H. Perrott

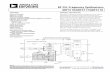

Popular VCO Structures

Vout

VinC RpL-Ramp

VCO Amp

Vout

Vin

LC oscillator

Ring oscillator

-1

LC Oscillator: low phase noise, large areaRing Oscillator: easy to integrate, higher phase noise

10M.H. Perrott

Model for Voltage to Frequency Mapping of VCO

Vout

VinC RpL-Ramp

VCO Amp

Vout

Vin

LC oscillator

Ring oscillator

-1VCO

Frequency

Input Voltage

slope=Kv

Vbias

vin

Fvco

Fout

v

fc

11M.H. Perrott

Time-domain frequency relationship (from previous slide)

Time-domain phase relationship

Model for Voltage to Phase Mapping of VCO

1/Fvco= α

1/Fvco= α+ε

out(t)

out(t)

Intuition of integral relationship between frequency and phase:

12M.H. Perrott

Frequency-Domain Model for VCO

Time-domain relationship (from previous slide)

Corresponding frequency-domain model

Laplace-Domain

out(t)

VCO

v(t) Φout(t)v(t) 2πKvs

VCO

Φout(t)v(t) Kvjf

VCO

Frequency-Domain

13M.H. Perrott

Divider

Implementation

Time-domain model- Frequency:

- Phase:

out div(t)

div(t)

out(t)

N

out(t)

count value

N = 6

Counter

14M.H. Perrott

Frequency-Domain Model of Divider

Time-domain relationship between VCO phase and divider output phase (from previous slide)

Corresponding frequency-domain model (same as Laplace-domain)

out(t) Φout(t)

NDivider

div(t) Φdiv(t)1

Divider

15M.H. Perrott

Phase Detector (PD)

XOR structure- Average value of error pulses corresponds to phase error- Loop filter extracts the average value and feeds to VCO

ref(t)

div(t)

e(t)

ref(t)

div(t)

e(t)1

-1

16M.H. Perrott

XOR Phase Detector Characteristic

Φref - Φdivππ/2−π/2−π 0

avg{e(t)}

1

-1

phase detectorrange = π

gain = 2/πgain = -2/π

1

-1e(t)

ref(t)

div(t)

W

1

-1e(t)

ref(t)

div(t)

W

W =Φref − Φdiv

π T/2

T/2 T/2

W = - Φref − Φdiv

π T/2

0 < Φref − Φdiv < π−π < Φref − Φdiv < 0

17M.H. Perrott

Frequency-Domain Model of XOR Phase Detector

Assume phase difference confined within 0 to π radians- Phase detector characteristic looks like a constant gain

element

Corresponding frequency-domain model

Φref - Φdivππ/2−π/2−π 0

avg{e(t)}

1

-1

gain = 2/πgain = -2/π

ref(t)PD

e(t)

PD gaindiv(t)

Φref(t)

Φdiv(t)

2π

e(t)

18M.H. Perrott

Loop Filter

Consists of a lowpass filter to extract average of phase detector error pulsesFrequency-domain model

First order example

C1

R1e(t) v(t)

Laplace-Domain

e(t) e(t)

VCO

e(t)

VCO

Frequency-Domain

v(t)v(t)H(s)

H(s)H(f)Loop

Filter

v(t)

19M.H. Perrott

Overall Linearized PLL Frequency-Domain Model

Combine models of individual components

N

Φref(t) Φout(t)

Φdiv(t)

e(t) v(t)H(s) 2πKv

s2π

1

Loop FilterXOR PD

VCO

Divider

N

Φref(t) Φout(t)

Φdiv(t)

e(t) v(t)H(f) Kv

jf2π

1

Laplace-Domain Model

Frequency-Domain Model

Loop FilterXOR PD

VCO

Divider

20M.H. Perrott

Open Loop versus Closed Loop Response

Frequency-domain model

Define A(f) as open loop responseN

Φref(t) Φout(t)

Φdiv(t)

e(t) v(t)H(f) Kv

jf2π

1

Loop FilterXOR PD

VCO

Divider

Define G(f) as a parameterizing closed loop function- More details later in this lecture

21M.H. Perrott

Classical PLL Transfer Function Design Approach

1. Choose an appropriate topology for H(f)Usually chosen from a small set of possibilities

2. Choose pole/zero values for H(f) as appropriate for the required filtering of the phase detector output

Constraint: set pole/zero locations higher than desired PLL bandwidth to allow stable dynamics to be possible

3. Adjust the open-loop gain to achieve the required bandwidth while maintaining stability

Plot gain and phase bode plots of A(f)Use phase (or gain) margin criterion to infer stability

22M.H. Perrott

Example: First Order Loop Filter

Overall PLL block diagram

Loop filter

N

Φref(t) Φout(t)

Φdiv(t)

e(t) v(t)H(f) Kv

jf2π

1

Loop FilterXOR PD

VCO

Divider

C1

R1e(t) v(t)

23M.H. Perrott

Closed Loop Poles Versus Open Loop Gain

Higher open loop gain leads to an increase in Q of closed loop poles

-90o

-180o

-120o

-150o

20log|A(f)|

f

angle(A(f))

Open loopgain

increased

0 dB

PM = 33o for C

PM = 45o for B

PM = 59o for A

A

A

A

B

B

B

C

C

C

Evaluation ofPhase Margin

Closed Loop PoleLocations of G(f)

Dominantpole pair

fp

Re{s}

Im{s}

0

24M.H. Perrott

Corresponding Closed Loop Response

Increase in open loop gain leads to- Peaking in closed loop frequency response- Ringing in closed loop step response

5 dB0 dB

-5 dB

f

A

C

fp

B

Frequency Response of G(f)

1.4

0

1

0.6

t

AB

C

Step Response of G(f)

25M.H. Perrott

The Impact of Parasitic Poles

Loop filter and VCO may have additional parasitic poles and zeros due to their circuit implementationWe can model such parasitics by including them in the loop filter transfer functionExample: add two parasitic poles to first order filter

C1

R1e(t) v(t)Parasitics

26M.H. Perrott

Closed Loop Poles Versus Open Loop Gain

-90o

-315o

-165o

-180o

-240o

20log|A(f)|

ffp3

angle(A(f))

Open loopgain

increased

0 dB

PM = 51o for B

PM = -12o for C

PM = 72o for A

Non-dominantpoles

Dominantpole pair

ABC

B

A

A

B

C

C

Evaluation ofPhase Margin

Closed Loop PoleLocations of G(f)

fp fp2

Re{s}

Im{s}

0

27M.H. Perrott

Corresponding Closed Loop Response

Increase in open loop gain now eventually leads to instability- Large peaking in closed loop frequency response- Increasing amplitude in closed loop step response

0 dB

Closed Loop Frequency Response Closed Loop Step Response

1

TimeFrequency

A

C

B

CB

A

28M.H. Perrott

Response of PLL to Divide Value Changes

Change in output frequency achieved by changing the divide valueClassical approach provides no direct model of impact of divide value variations- Treat divide value variation as a perturbation to a linear

systemPLL responds according to its closed loop response

N

Φref(t) Φout(t)

Φdiv(t)

e(t) v(t)H(f) Kv

jf2π

1

Loop FilterXOR PD

VCO

Divider

NN+1

t

29M.H. Perrott

Response of an Actual PLL to Divide Value Change

Example: Change divide value by one

40 60 80 100 120 140 160 180 200 220 24091.8

92

92.2

92.4

92.6

92.8

93

N (

Div

ide

Val

ue)

Synthesizer Response To Divider Step

40 60 80 100 120 140 160 180 200 220 2401.83

1.84

1.85

1.86

1.87

Out

put F

requ

ency

(G

Hz)

Time (microseconds)

- PLL responds according to closed loop response!

30M.H. Perrott

What Happens with Large Divide Value Variations?

PLL temporarily loses frequency lock (cycle slipping occurs)

- Why does this happen?

40 60 80 100 120 140 160 180 200 220 240

92

93

94

95

96N

(D

ivid

e V

alue

)

Synthesizer Response To Divider Step

40 60 80 100 120 140 160 180 200 220 240

1.84

1.86

1.88

1.9

1.92

Out

put F

requ

ency

(G

Hz)

Time (microseconds)

31M.H. Perrott

Recall Phase Detector Characteristic

To simplify modeling, we assumed that we always operated in a confined phase range (0 to π)- Led to a simple PD model

Large perturbations knock us out of that confined phase range- PD behavior varies depending on the phase range it

happens to be in

Φref - Φdivππ/2−π/2−π 0

avg{e(t)}

1

-1

gain = 2/πgain = -2/π

32M.H. Perrott

Cycle Slipping

Consider the case where there is a frequency offset between divider output and reference- We know that phase difference will accumulate

Resulting ramp in phase causes PD characteristic to be swept across its different regions (cycle slipping)

Φref - Φdivππ/2−π/2−π 0

avg{e(t)}

1

-1

gain = 2/πgain = -2/π

ref(t)

div(t)

33M.H. Perrott

Impact of Cycle Slipping

Loop filter averages out phase detector outputSevere cycle slipping causes phase detector to alternate between regions very quickly- Average value of XOR characteristic can be close to

zero- PLL frequency oscillates according to cycle slipping- In severe cases, PLL will not re-lock

PLL has finite frequency lock-in range!

π−π 3π nπ (n+2)π

1

-1

XOR DC characteristiccycle slipping

Φref - Φdiv

34M.H. Perrott

Back to PLL Response Shown Previously

PLL output frequency indeed oscillates- Eventually locks when frequency difference is small enough

- How do we extend the frequency lock-in range?

40 60 80 100 120 140 160 180 200 220 240

92

93

94

95

96

N (

Div

ide

Val

ue)

Synthesizer Response To Divider Step

40 60 80 100 120 140 160 180 200 220 240

1.84

1.86

1.88

1.9

1.92

Out

put F

requ

ency

(G

Hz)

Time (microseconds)

35M.H. Perrott

Phase Frequency Detectors (PFD)

D

Q

Q

D

Q

Q

R

Rref(t)

div(t)

Ref(t)

Div(t)

1

1

up(t)

e(t)

down(t)

Up(t)

Down(t)

10

-1

E(t)

Example: Tristate PFD

36M.H. Perrott

Tristate PFD Characteristic

Calculate using similar approach as used for XOR phase detector

Note that phase error characteristic is asymmetric about zero phase- Key attribute for enabling frequency detection

2π−2π

1

−1

avg{e(t)}

phase detectorrange = 4π

gain = 1/(2π)

Φref - Φdiv

37M.H. Perrott

PFD Enables PLL to Always Regain Frequency Lock

Asymmetric phase error characteristic allows positive frequency differences to be distinguished from negative frequency differences - Average value is now positive or negative according to

sign of frequency offset- PLL will always relock

Φref - Φdiv2π 4π 2nπ−2π

1

-1

Tristate DC characteristic

cycle slipping

0

lock

38M.H. Perrott

Another PFD Structure

XOR-based PFD

S

R

D

Q

Q

D

Q

Q

D

Q

Q

D

Q

Q

ref(t)

div(t)

e(t)

Divide-by-2 FrequencyDetector

PhaseDetector

ref(t)

div(t)

ref/2(t)

div/2(t)

-11

e(t)

ref/2(t)

div/2(t)

39M.H. Perrott

XOR-based PFD Characteristic

Calculate using similar approach as used for XOR phase detector

Phase error characteristic asymmetric about zero phase- Average value of phase error is positive or negative during

cycle slipping depending on sign of frequency error

2ππ−2π 5π4π−3π

1

−1

avg{e(t)}

phase detectorrange = 2π

gain = 1/π

Φref - Φdiv0

40M.H. Perrott

Linearized PLL Model With PFD Structures

Assume that when PLL in lock, phase variations are within the linear range of PFD- Simulate impact of cycle slipping if desired (do not

include its effect in model)Same frequency-domain PLL model as before, but PFD gain depends on topology used

N

Φref(t) Φout(t)

Φdiv(t)

e(t) v(t)H(f) Kv

jfα2π

1

Loop FilterPFD

VCO

Divider

Tristate: α=1XOR-based: α=2

41M.H. Perrott

Type I versus Type II PLL Implementations

Type I: one integrator in PLL open loop transfer function- VCO adds on integrator- Loop filter, H(f), has no integrators

Type II: two integrators in PLL open loop transfer function- Loop filter, H(f), has one integrator

N

Φref(t) Φout(t)

Φdiv(t)

e(t) v(t)H(f) Kv

jfα2π

1

Loop FilterPFD

VCO

Divider

Tristate: α=1XOR-based: α=2

42M.H. Perrott

DC output range of gain block versus integrator

Issue: DC gain of loop filter often small and PFD output range is limited- Loop filter output fails to cover full input range of VCO

VCO Input Range Issue for Type I PLL Implementations

PFDLoopFilter

N[k]

ref(t) out(t)

Divider

e(t) v(t)

VDD

Gnd

Output Rangeof Loop Filter

NoIntegrator

VCO

0Ks

Integrator0

Gain Block

K

43M.H. Perrott

Options for Achieving Full Range Span of VCO

LoopFilter

D/A

e(t) v(t)C.P.

VDD

Gnd

Output Rangeof Loop FilterCourse

Tune

NoIntegrator

LoopFilter

e(t) v(t)C.P.

VDD

Gnd

Output Rangeof Loop Filter

ContainsIntegrator

Type I Type II

Type I- Add a D/A converter to provide coarse tuning

Adds power and complexitySteady-state phase error inconsistently set

Type II- Integrator automatically provides DC level shifting

Low power and simple implementationSteady-state phase error always set to zero

44M.H. Perrott

A Common Loop Filter for Type II PLL Implementation

Use a charge pump to create the integrator- Current onto a capacitor forms integrator- Add extra pole/zero using resistor and capacitor

Gain of loop filter can be adjusted according to the value of the charge pump currentExample: lead/lag network

C1C2

R1

v(t)e(t) ChargePump

i(t)

45M.H. Perrott

Charge Pump Implementations

Switch currents in and out:

e(t)down(t) e(t)

Iout(t)Iout(t)

Icp

Icp 2Icp

Icp Icp

Single-Ended Differential

up(t)

46M.H. Perrott

Modeling of Loop Filter/Charge Pump

Charge pump is gain elementLoop filter forms transfer function

Example: lead/lag network from previous slide

e(t) v(t)H(s)Icp

LoopFilter

ChargePump

47M.H. Perrott

PLL Design with Lead/Lag Filter

Overall PLL block diagram

Loop filter

Set open loop gain to achieve adequate phase margin- Set fz lower than and fp higher than desired PLL bandwidth

N

Φref(t) Φout(t)

Φdiv(t)

e(t) v(t)H(f) Kv

jfα2π

1

Loop FilterPFD

VCO

Divider

Tristate: α=1XOR-based: α=2

Icp

ChargePump

48M.H. Perrott

Closed Loop Poles Versus Open Loop Gain

Open loop gain cannot be too low or too high if reasonable phase margin is desired

Non-dominantpole

Dominantpole pair

Open loopgain

increased

120o

-180o

-140o

-160o

20log|A(f)|

ffz

0 dB

PM = 55o for CPM = 53o for APM = 54o for B

angle(A(f))

A

A

A

A

B

B

B

B

C

C

C

C

Evaluation ofPhase Margin

Closed Loop PoleLocations of G(f)

fp

Re{s}

Im{s}

0

49M.H. Perrott

Impact of Parasitics When Lead/Lag Filter Used

We can again model impact of parasitics by including them in loop filter transfer function

Example: include two parasitic poles with the lead/lag transfer function

C1C2

R1

e(t) ChargePump

i(t) v(t)Parasitics

50M.H. Perrott

Closed Loop Poles Versus Open Loop Gain

Closed loop response becomes unstable if open loop gain is too high

Non-dominantpoles

Dominantpole pair

Open loopgain

increased

120o

-180o

-140o

-160o

20log|A(f)|

ffz

0 dB

PM = -7o for C

PM = 38o for BPM = 46o for A

angle(A(f))

A

A

AA

B

B

B

B

C

C

C

C

Evaluation ofPhase Margin

Closed Loop PoleLocations of G(f)

Re{s}

Im{s}

0

fp2fp fp3

51M.H. Perrott

Negative Issues For Type II PLL Implementations

Parasitic pole/zero pair causes- Peaking in the closed loop frequency response- Extended settling time due to parasitic “tail” response

Bad for wireless systems demanding fast settling time

ffofz

fzfcp

|G(f)|Peaking caused by

undesired pole/zero pair

0

1

Frequency (Hz)

0 1 2 3 4

0.6

1

1.4

Normalized time: t*fo

Nor

mal

ized

Am

plitu

de

Step Responses for a Second OrderG(f) implemented as a Bessel Filter

Type II: fz/fo = 1/3

Type II: fz/fo = 1/8

Type I

52M.H. Perrott

Summary of Integer-N Dynamic Modeling

Linearized models can be derived for each PLL block- Resulting transfer function model of PLL is accurate for

small perturbations in PLL- Linear PLL model breaks down for large perturbations

on PLL, such as a large step change in frequencyCycle slipping is key nonlinear effect

Key issues for designing PLL are- Achieve stable operation with desired bandwidth- Allow full range of VCO with a simple implementation

Type II PLL is very popular to achieve this

53M.H. Perrott

Frequency Synthesizer Noise in Wireless Systems

Synthesizer noise has a negative impact on system- Receiver – lower sensitivity, poorer blocking performance- Transmitter – increased spectral emissions (output spectrum

must meet a mask requirement)Noise is characterized in frequency domain

Zin

Zo LNA To Filter

From Antennaand Bandpass

Filter

PC boardtrace

PackageInterface

LO signal

MixerRF in IF out

FrequencySynthesizer

ReferenceFrequency

VCO

f

PhaseNoise

fo

54M.H. Perrott

Phase noise is non-periodic

- Described as a spectral density relative to carrier power

Spurious noise is periodic

- Described as tone power relative to carrier power

Phase Noise Versus Spurious Noise

SΦout(f)Sout(f)

f-fo fo

1dBc/Hz

Sout(f)

f-fo fo

dBc1

fspur

21 dspur

fspur

2

55M.H. Perrott

Sources of Noise in Frequency Synthesizers

Extrinsic noise sources to VCO- Reference/divider jitter and reference feedthrough- Charge pump noise

PFD ChargePump

e(t) v(t)

N

LoopFilter

DividerVCO

ref(t)

div(t)

f

Charge PumpNoise

VCO Noise

f

-20 dB/dec

1/Tf

ReferenceJitter

f

ReferenceFeedthrough

T

f

DividerJitter

56M.H. Perrott

Modeling the Impact of Noise on Output Phase of PLL

Determine impact on output phase by deriving transfer function from each noise source to PLL output phase- There are a lot of transfer functions to keep track of!

Φdiv[k]

Φref [k] KV

jf

v(t) Φout(t)H(f)

1N

�πα e(t)

espur(t)Φjit[k] Φvn(t)Ιcpn(t)

Icp

VCO Noise

f0

SΦjit(f)

f0

SΙcpn(f)

f0

SEspur(f)

Divider/ReferenceJitter

ReferenceFeedthrough

Charge PumpNoise

1/T f0

SΦvn(f)

-20 dB/dec

PFDChargePump

LoopFilter

Divider

VCO

57M.H. Perrott

Simplified Noise Model

Refer all PLL noise sources (other than the VCO) to the PFD output- PFD-referred noise corresponds to the sum of these

noise sources referred to the PFD output

Φdiv[k]

Φref [k] KV

jf

v(t) Φout(t)H(f)

1N

�πα e(t)

Φvn(t)en(t)

Icp

VCO-referredNoise

f0

SEn(f)

PFD-referredNoise

1/T f0

SΦvn(f)

-20 dB/dec

PFDChargePump

LoopFilter

Divider

VCO

58M.H. Perrott

Impact of PFD-referred Noise on Synthesizer Output

Transfer function derived using Black’s formula

Φdiv[k]

Φref [k] KV

jf

v(t) Φout(t)H(f)

1N

�πα e(t)

Φvn(t)en(t)

Icp

VCO-referredNoise

f0

SEn(f)

PFD-referredNoise

1/T f0

SΦvn(f)

-20 dB/dec

PFDChargePump

LoopFilter

Divider

VCO

59M.H. Perrott

Impact of VCO-referred Noise on Synthesizer Output

Transfer function again derived from Black’s formula

Φdiv[k]

Φref [k] KV

jf

v(t) Φout(t)H(f)

1N

�πα e(t)

Φvn(t)en(t)

Icp

VCO-referredNoise

f0

SEn(f)

PFD-referredNoise

1/T f0

SΦvn(f)

-20 dB/dec

PFDChargePump

LoopFilter

Divider

VCO

60M.H. Perrott

A Simpler Parameterization for PLL Transfer Functions

Define G(f) as

- A(f) is the open loop transfer function of the PLL

Φdiv[k]

Φref [k] KV

jf

v(t) Φout(t)H(f)

1N

�πα e(t)

Φvn(t)en(t)

Icp

VCO-referredNoise

f0

SEn(f)

PFD-referredNoise

1/T f0

SΦvn(f)

-20 dB/dec

PFDChargePump

LoopFilter

Divider

VCO

Always has a gainof one at DC

61M.H. Perrott

Parameterize Noise Transfer Functions in Terms of G(f)

PFD-referred noise

VCO-referred noise

62M.H. Perrott

Parameterized PLL Noise Model

PFD-referred noise is lowpass filteredVCO-referred noise is highpass filteredBoth filters have the same transition frequency values- Defined as fo

Φvn(t)en(t)

Φout(t)Φc(t)Φn(t)

Φnvco(t)Φnpfd(t)

fo1-G(f)

foG(f)�πNα

VCO-referredNoise

f0

SEn(f)

PFD-referredNoise

1/T f0

SΦvn(f)

-20 dB/dec

Divider Controlof Frequency Setting

(assume noiseless for now)

63M.H. Perrott

Impact of PLL Parameters on Noise Scaling

PFD-referred noise is scaled by square of divide value and inverse of PFD gain- High divide values lead to large multiplication of this noise

VCO-referred noise is not scaled (only filtered)

Φvn(t)en(t)

Φout(t)Φc(t)Φn(t)

Φnvco(t)Φnpfd(t)

fo1-G(f)

foG(f)�πNα

VCO-referredNoise

f0

SEn(f)

PFD-referredNoise

1/T f0

SΦvn(f)

-20 dB/dec

Divider Controlof Frequency Setting

(assume noiseless for now)

Sen(f)�πNα

2

Rad

ians

2 /Hz

SΦvn(f)

f0

64M.H. Perrott

Optimal Bandwidth Setting for Minimum Noise

Optimal bandwidth is where scaled noise sources meet- Higher bandwidth will pass more PFD-referred noise- Lower bandwidth will pass more VCO-referred noise

Φvn(t)en(t)

Φout(t)Φc(t)Φn(t)

Φnvco(t)Φnpfd(t)

fo1-G(f)

foG(f)�πNα

VCO-referredNoise

f0

SEn(f)

PFD-referredNoise

1/T f0

SΦvn(f)

-20 dB/dec

Divider Controlof Frequency Setting

(assume noiseless for now)

Sen(f)�πNα

2

Rad

ians

2 /Hz

SΦvn(f)

f(fo)opt0

65M.H. Perrott

Resulting Output Noise with Optimal Bandwidth

PFD-referred noise dominates at low frequencies- Corresponds to close-in phase noise of synthesizer

VCO-referred noise dominates at high frequencies- Corresponds to far-away phase noise of synthesizer

Φvn(t)en(t)

Φout(t)Φc(t)Φn(t)

Φnvco(t)Φnpfd(t)

fo1-G(f)

foG(f)�πNα

VCO-referredNoise

f0

SEn(f)

PFD-referredNoise

1/T f0

SΦvn(f)

-20 dB/dec

Divider Controlof Frequency Setting

(assume noiseless for now)

Sen(f)�πNα

2

Rad

ians

2 /Hz

SΦvn(f)

f(fo)opt0

Rad

ians

2 /Hz SΦnpfd(f)

SΦnvco(f)

f(fo)opt0

66M.H. Perrott

Summary of Noise Analysis of Integer-N Synthesizers

Key PLL noise sources are- VCO noise- PFD-referred noise

Charge pump noise, reference noise, etc.

Setting of PLL bandwidth has strong impact on noise- High PLL bandwidth suppresses VCO noise- Low PLL bandwidth suppresses PFD-referred noise

67M.H. Perrott

Fractional-N Frequency Synthesis

Divide value is dithered between integer valuesFractional divide values can be realized!

Very high frequency resolution

PFDChargePump

Nsd[k]

out(t)e(t)

DitheringModulator

v(t)

N[k]

LoopFilter

Divider

VCO

ref(t)

div(t)

M

M+1

Fout = M.F Fref

M.F

Fref

Kingsford-SmithUS Patent 3,928,813

1974 (filing date)

68M.H. Perrott

Outline of Fractional-N Synthesizers

Traditional ApproachSigma-Delta ConceptsSynthesizer Noise Analysis

69M.H. Perrott

Classical Fractional-N Synthesizer Architecture

Use an accumulator to perform dithering operation- Fractional input value fed into accumulator- Carry out bit of accumulator fed into divider

1-bit

PFD LoopFilter

ref(t)

div(t)

out(t)

frac[k]Accumulator

N/N+1

carry_out[k]

e(t)

Nsd[k] = N + frac[k]

70M.H. Perrott

Accumulator Operation

Carry out bit is asserted when accumulator residue reaches or surpasses its full scale value- Accumulator residue increments by input fractional

value each clock cycle

residue[k]

carry_out[k]

frac[k] =.25

1-bitM-bit

M-bitfrac[k]

Accumulatorcarry_out[k]

residue[k]

clk(t)

71M.H. Perrott

Fractional-N Synthesizer Signals with N = 4.25

Divide value set at N = 4 most of the time - Resulting frequency offset causes phase error to

accumulate- Reset phase error by “swallowing” a VCO cycle

Achieved by dividing by 5 every 4 reference cycles

phase error(t)

carry_out(t)

out(t)

div(t)

ref(t)

e(t)

72M.H. Perrott

The Issue of Spurious Tones

PFD error is periodic- Note that actual PFD waveform is series of pulses – the

sawtooth waveform represents pulse width values over timePeriodic error signal creates spurious tones in synthesizer output- Ruins noise performance of synthesizer

1-bit

PFD LoopFilter

ref(t)

div(t)

out(t)

frac[k]Accumulator

N/N+1

carry_out[k]

e(t)

Nsd[k] = N + frac[k]

73M.H. Perrott

The Phase Interpolation Technique

Phase error due to fractional technique is predicted by the instantaneous residue of the accumulator- Cancel out phase error based on accumulator residue

1-bitM-bit

M-bit

PFD LoopFilter

ref(t)

div(t)

out(t)

frac[k]Accumulator

N/N+1

carry_out[k]

e(t)

D/A

residue[k]

α

74M.H. Perrott

The Problem With Phase Interpolation

Gain matching between PFD error and scaled D/A output must be extremely precise- Any mismatch will lead to spurious tones at PLL output

1-bitM-bit

M-bit

PFD LoopFilter

ref(t)

div(t)

out(t)

frac[k]Accumulator

N/N+1

carry_out[k]

e(t)

D/A

residue[k]

α

Is There a Better Way?

76M.H. Perrott

A Better Dithering Method: Sigma-Delta Modulation

Sigma-Delta dithers in a manner such that resulting quantization noise is “shaped” to high frequencies

M-bit Input 1-bitD/A

Analog Output

Input

QuantizationNoise

Digital InputSpectrum

Analog OutputSpectrum

Time Domain

Frequency Domain

Σ−Δ

Digital Σ−ΔModulator

77M.H. Perrott

Linearized Model of Sigma-Delta Modulator

Composed of two transfer functions relating input and noise to output- Signal transfer function (STF)

Filters input (generally undesirable)- Noise transfer function (NTF)

Filters (i.e., shapes) noise that is assumed to be white

x[k] y[k] y[k]x[k]q[k]

r[k]

z=ej2πfT

z=ej2πfT

NTF

STF

Σ−Δ

Hn(z)

Hs(z)

1

Sr(ej2πfT)= 112

Sq(ej2πfT)= |Hn(ej2πfT)|2112

78M.H. Perrott

Example: Cutler Sigma-Delta Topology

Output is quantized in a multi-level fashionError signal, e[k], represents the quantization errorFiltered version of quantization error is fed back to input- H(z) is typically a highpass filter whose first tap value is 1

i.e., H(z) = 1 + a1z-1 + a2 z-2 L

- H(z) – 1 therefore has a first tap value of 0Feedback needs to have delay to be realizable

x[k] u[k]

e[k]

y[k]

H(z) - 1

79M.H. Perrott

Linearized Model of Cutler Topology

Represent quantizer block as a summing junction in which r[k] represents quantization error- Note:

It is assumed that r[k] has statistics similar to white noise- This is a key assumption for modeling – often not true!

x[k] u[k]

e[k]

y[k]

H(z) - 1

x[k] u[k]r[k]

e[k]

y[k]

H(z) - 1

80M.H. Perrott

Calculation of Signal and Noise Transfer Functions

Calculate using Z-transform of signals in linearizedmodel

- NTF: Hn(z) = H(z)- STF: Hs(z) = 1

x[k] u[k]

e[k]

y[k]

H(z) - 1

x[k] u[k]r[k]

e[k]

y[k]

H(z) - 1

81M.H. Perrott

A Common Choice for H(z)

m = 1

m = 2

m = 3

Mag

nitu

de

0Frequency (Hz)

1/(2T)

8

7

6

5

4

3

2

1

0

82M.H. Perrott

Example: First Order Sigma-Delta Modulator

Choose NTF to be

Plot of output in time and frequency domains with input of

00

Am

plitu

de

Mag

nitu

de (d

B)

Sample Number 200 0

1

Frequency (Hz) 1/(2T)

x[k] u[k]

e[k]

y[k]

H(z) - 1

83M.H. Perrott

Example: Second Order Sigma-Delta Modulator

Choose NTF to be

Plot of output in time and frequency domains with input of

x[k] u[k]

e[k]

y[k]

H(z) - 1

Mag

nitu

de (d

B)

0 Sample Number 200 0-1

Am

plitu

de

2

1

0

Frequency (Hz) 1/(2T)

84M.H. Perrott

Example: Third Order Sigma-Delta Modulator

Choose NTF to be

Plot of output in time and frequency domains with input of

x[k] u[k]

e[k]

y[k]

H(z) - 1

Mag

nitu

de (d

B)

0 0Sample Number 200

Am

plitu

de

4

3

2

1

0

-1

-2

-3Frequency (Hz) 1/(2T)

85M.H. Perrott

Observations

Low order Sigma-Delta modulators do not appear to produce “shaped” noise very well- Reason: low order feedback does not properly

“scramble” relationship between input and quantization noise

Quantization noise, r[k], fails to be whiteHigher order Sigma-Delta modulators provide much better noise shaping with fewer spurs- Reason: higher order feedback filter provides a much

more complex interaction between input and quantization noise

86M.H. Perrott

Warning: Higher Order Modulators May Still Have Tones

Quantization noise, r[k], is best whitened when a “sufficiently exciting” input is applied to the modulator- Varying input and high order helps to “scramble”

interaction between input and quantization noiseWorst input for tone generation are DC signals that are rational with a low valued denominator- Examples (third order modulator with no dithering):

Mag

nitu

de (d

B)

0 Frequency (Hz) 1/(2T)

Mag

nitu

de (d

B)

0 Frequency (Hz) 1/(2T)

x[k] = 0.1 x[k] = 0.1 + 1/1024

87M.H. Perrott

Fractional Spurs Can Be Theoretically Eliminated

See:- M. Kozak, I. Kale, “Rigorous Analysis of Delta-Sigma

Modulators for Fractional-N PLL Frequency Synthesis”, IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, vol. 51, no. 6, pp. 1148-1162, June 2004.

- S. Pamarti, I. Galton, "LSB Dithering in MASH Delta–Sigma D/A Converters", IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 54, no. 4, pp. 779 –790, April 2007.

88M.H. Perrott

MASH topology

Cascade first order sectionsCombine their outputs after they have passed through digital differentiators

Advantage over single loop approach- Allows pipelining to be applied to implementation

High speed or low power applications benefit

x[k]

y[k]

r1[k]ΣΔM1[k]

y1[k]

r2[k]ΣΔM2[k]

y2[k]

u[k]

ΣΔM3[k]

y3[k]

M 1 1

1-z-1 (1-z-1)2

89M.H. Perrott

Calculation of STF and NTF for MASH topology (Step 1)

Individual output signals of each first order modulator

Addition of filtered outputs

x[k]

y[k]

r1[k]ΣΔM1[k]

y1[k]

r2[k]ΣΔM2[k]

y2[k]

u[k]

ΣΔM3[k]

y3[k]

M 1 1

1-z-1 (1-z-1)2

90M.H. Perrott

Calculation of STF and NTF for MASH topology (Step 1)

Overall modulator behavior

- STF: Hs(z) = 1- NTF: Hn(z) = (1 – z-1)3

x[k]

y[k]

r1[k]ΣΔM1[k]

y1[k]

r2[k]ΣΔM2[k]

y2[k]

u[k]

ΣΔM3[k]

y3[k]

M 1 1

1-z-1 (1-z-1)2

91M.H. Perrott

Sigma-Delta Frequency Synthesizers

Use Sigma-Delta modulator rather than accumulator to perform dithering operation- Achieves much better spurious performance than

classical fractional-N approach

PFD ChargePump

Nsd[m]

out(t)e(t)

Σ−ΔModulator

v(t)

N[m]

LoopFilter

DividerVCO

ref(t)

div(t)

MM+1

Fout = M.F Fref

f

Σ−ΔQuantization

Noise

Fref

Riley et. al.,JSSC, May 1993

92M.H. Perrott

The Need for A Better PLL Model

Classical PLL model- Predicts impact of PFD and VCO referred noise sources- Does not allow straightforward modeling of impact due

to divide value variationsThis is a problem when using fractional-N approach

Φdiv[k]

Φref [k] KV

jf

v(t) Φout(t)H(f)

1N

�πα e(t)

Φvn(t)en(t)

Icp

VCO-referredNoise

f0

SEn(f)

PFD-referredNoise

1/T f0

SΦvn(f)

-20 dB/dec

PFDChargePump

LoopFilterDivider

VCO

N[k]

93M.H. Perrott

Fractional-N PLL Model

Perrott et. al. JSSC, Aug. 2002

Closed loop dynamics parameterized by

Φdiv[k]

Φref[k] KV

jf

v(t) Φout(t)H(f)

1Nnom

2π z-1

z=ej2πfT1 - z-1n[k]

T1

Φd[k]

T2π

e(t)

PFD

Divider

LoopFilterC.P. VCO

α

Tristate: α=1XOR: α=2

Icp

en(t)f

0

SEn(f)

PFD-referredNoise

1/TΦvn(t)

VCO-referredNoise

f0

SΦvn(f)

-20 dB/dec

Sq(ej2πfT)

f0

Σ−ΔQuantization

Noise

94M.H. Perrott

Parameterized PLL Noise Model

Design revolves around choice of Σ−Δ and G(f)- We will focus on G(f) design here

Φvn(t)

T G(f)

2π z-1

1 - z-1

n[k] Φn[k]

En(t)

Φout(t)Φdiv(t)Φtn,pll(t)

fo1-G(f)

fo

fo

G(f)2π

Nnom

z=ej2πfT

α

f0

f0

SEn(f)

Sq(ej2πfT)

SΦvn

(f)

1/T

f0

PFD-referredNoise

VCO-referredNoise

Σ−Δ

QuantizationNoise

-20 dB/dec

95M.H. Perrott

A Well Designed Sigma-Delta Synthesizer

Order of G(f) is set to equal to the Sigma-Delta order- Sigma-Delta noise falls at -20 dB/dec above G(f) bandwidth

Bandwidth of G(f) is set low enough such that synthesizer noise is dominated by intrinsic PFD and VCO noise

-160

-150

-140

-130

-120

-110

-100

-90

-80

-70

-60

Frequency

Spe

ctra

l Den

sity

(dB

c/H

z)

f0 1/T

10 kHz 100 kHz 1 MHz 10 MHz

PFD-referrednoise

SΦout,En(f)

VCO-referred noise

SΦout,vn(f)

Σ−Δnoise

SΦout,ΔΣ(f)

fo = 84 kHz

96M.H. Perrott

Impact of Increased PLL Bandwidth

Allows more PFD noise to pass throughAllows more Sigma-Delta noise to pass throughIncreases suppression of VCO noise

-160

-150

-140

-130

-120

-110

-100

-90

-80

-70

-60

Frequency

Spe

ctra

l Den

sity

(dB

c/H

z)

f0 1/T

10 kHz 100 kHz 1 MHz 10 MHz

PFD-referrednoise

SΦout,En(f)

VCO-referred noise

SΦout,vn(f)

Σ−Δnoise

SΦout,ΔΣ(f)

f0 1/T

10 kHz 100 kHz 1 MHz 10 MHz

Frequency

-160

-150

-140

-130

-120

-110

-100

-90

-80

-70

-60

Spe

ctra

l Den

sity

(dB

c/H

z)

PFD-referrednoise

SΦout,En(f)

VCO-referred noise

SΦout,vn(f)

Σ−Δnoise

SΦout,ΔΣ(f)

fo = 84 kHz fo = 160 kHz

97M.H. Perrott

Impact of Increased Sigma-Delta Order

PFD and VCO noise unaffectedSigma-Delta noise no longer attenuated by G(f) such that a -20 dB/dec slope is achieved above its bandwidth

-160

-150

-140

-130

-120

-110

-100

-90

-80

-70

-60

Frequency

Spe

ctra

l Den

sity

(dB

c/H

z)

f0 1/T

10 kHz 100 kHz 1 MHz 10 MHz

PFD-referrednoise

SΦout,En(f)

VCO-referred noise

SΦout,vn(f)

Σ−Δnoise

SΦout,ΔΣ(f)

-160

-150

-140

-130

-120

-110

-100

-90

-80

-70

-60

Spe

ctra

l Den

sity

(dB

c/H

z)f0 1/T

10 kHz 100 kHz 1 MHz 10 MHz

PFD-referrednoise

SΦout,En(f)

VCO-referred noise

SΦout,vn(f)

Σ−Δnoise

SΦout,ΔΣ(f)

Frequency

m = 2 m = 3

98M.H. Perrott

Impact of Σ−Δ Quantization Noise on Synth. Output

PFD LoopFilter

N/N+1

Ref Out

M-bit 1-bit

Div

Σ−ΔModulator

Fout

Noise

FrequencySelection

FrequencySelection

OutputSpectrum

QuantizationNoise Spectrum

PLL dynamicsΣ−Δ

Lowpass action of PLL dynamics suppresses the shaped Σ-Δ quantization noise

99M.H. Perrott

Impact of Increasing the PLL Bandwidth

Higher PLL bandwidth leads to less quantization noise suppression

PFD LoopFilter

N/N+1

Ref Out

M-bit 1-bit

Div

Σ−ΔModulator

Fout

Noise

FrequencySelection

FrequencySelection

OutputSpectrum

QuantizationNoise Spectrum

PLL dynamicsΣ−Δ

Tradeoff: Noise performance vs PLL bandwidth

100M.H. Perrott

A Cancellation Method for Reducing Quantization Noise

Key idea: quantization noise can be predicted within the digital Σ−Δ modulator structureIssue: cancellation is limited by analog matching- Achieves < 20 dB cancellation in practice

PFD ChargePump

Nsd[k]

out(t)r(t)

Σ−ΔModulator

v(t)

N[k]

LoopFilter

DividerVCO

ref(t)

div(t)

f

Σ−Δ QuantizationNoise SuppressionDAC

q[k]

e(t)

Pamarti et. al.,TCAS II, Nov 2003

101M.H. Perrott

Improved Cancellation Through Inherent Matching

Combined PFD/DAC structure achieves inherent matching between error and cancellation signal- > 29 dB quantization noise cancellation achieved

PFD/DAC

Nsd[k]

out(t)r(t)

Σ−ΔModulator

v(t)

N[k]

LoopFilter

DividerVCO

ref(t)

div(t)

f

Σ−Δ QuantizationNoise Suppression

q[k]

Meninger et. al.,TCAS II, Nov 2003

102M.H. Perrott

Improved Cancellation Through Continuous Calibration

Gain of DAC is adjusted in an adaptive manner using LMS algorithm- > 30 dB noise cancellation achieved

PFD ChargePump

Nsd[k]

out(t)r(t)

Σ−ΔModulator

v(t)

N[k]

LoopFilter

DividerVCO

ref(t)

div(t)

f

Σ−Δ QuantizationNoise SuppressionDAC

q[k]

e(t)

LMS Algorithm

gain

Gupta et. al.,ISSCC, Feb 2006

103M.H. Perrott

Summary of Fractional-N Frequency Synthesizers

Fractional-N synthesizers allow very high resolution to be achieved with relatively high reference frequencies- Cost is introduction of quantization noise due to dithering

of dividerClassical fractional-N synthesizers used an accumulator for dithering- Quantization noise cancellation was attempted

Sigma-Delta fractional-N synthesizers improve quantization noise by utilizing noise shaping techniques- Key tradeoff: PLL bandwidth versus phase noise- Quantization noise cancellation has made a comeback

Related Documents