-

7/29/2019 HDL based Simulation of digital RF Frequency Synthesizers

1/20

Andreas NeyerSeptember 2005

BMAS 2005 1

HDL based Simulation of digital RF FrequencySynthesizers

A. Neyer, S. Sappok, S. Heinen

Chair of Integrated Analog Circuits

RWTH Aachen University

-

7/29/2019 HDL based Simulation of digital RF Frequency Synthesizers

2/20

Chair of Integrated Analog Circuits

Andreas NeyerBMAS 2005

HDL based Simulation of digital RF Frequency Synthesizers 2

Outline

Motivation

Demonstration Example: All-digital PLL for GSM systems

Requirements in modeling RF-transceivers

Design flow overview

Abstract connectivity modeling for RF applications

Summary

-

7/29/2019 HDL based Simulation of digital RF Frequency Synthesizers

3/20

Chair of Integrated Analog Circuits

Andreas NeyerBMAS 2005

HDL based Simulation of digital RF Frequency Synthesizers 3

Motivation

RF CMOS circuit implementation reaches nanometer scale

Challenges for analog RF CMOS implementation

Co-integration of digital baseband and analog RF circuits

Advanced design and verification tools

Advanced modeling techniques

(Our target) HDL modeling of RF circuits

Connectivity verification High performance transient simulation

-

7/29/2019 HDL based Simulation of digital RF Frequency Synthesizers

4/20

Chair of Integrated Analog Circuits

Andreas NeyerBMAS 2005

HDL based Simulation of digital RF Frequency Synthesizers 4

RF Circuits in Nanometer CMOS

Challenges for analog RF CMOS scaling

Limited scaling qualities compared to digital circuits Low voltage headroom

Increased non-idealities and manufacturing tolerances

Analog signals are sensitive to noise

Degraded signal-to-noise ratio

RF architectures suited nanometer CMOS

-

7/29/2019 HDL based Simulation of digital RF Frequency Synthesizers

5/20

Chair of Integrated Analog Circuits

Andreas NeyerBMAS 2005

HDL based Simulation of digital RF Frequency Synthesizers 5

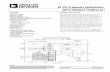

CPPFD

VCOloop filter

reference

clock Buffer

N

modulator

pre-

compensationpulse filter

channel selection

data

Typical Mixed-Signal PLL Architecture

analog

digital

-

7/29/2019 HDL based Simulation of digital RF Frequency Synthesizers

6/20

Chair of Integrated Analog Circuits

Andreas NeyerBMAS 2005

HDL based Simulation of digital RF Frequency Synthesizers 6

Demonstration Example: All-digital PLL

+

chf

+ NCO

ref2

K

f

reff

E

-

7/29/2019 HDL based Simulation of digital RF Frequency Synthesizers

7/20

Chair of Integrated Analog Circuits

Andreas NeyerBMAS 2005

HDL based Simulation of digital RF Frequency Synthesizers 7

Demonstration Example: All-digital PLL

NCO

ref2

K

f

reff

E

analog

-

7/29/2019 HDL based Simulation of digital RF Frequency Synthesizers

8/20

Chair of Integrated Analog Circuits

Andreas NeyerBMAS 2005

HDL based Simulation of digital RF Frequency Synthesizers 8

Simulation & Post-Processing

All-digital PLL implemented as pure VHDL model

Simulation using two different simulators

Event-triggered simulator

Mixed-signal simulator

MATLAB for post-processing

Phase error calculation

Eye-diagram PSD calculation

-

7/29/2019 HDL based Simulation of digital RF Frequency Synthesizers

9/20

Chair of Integrated Analog Circuits

Andreas NeyerBMAS 2005

HDL based Simulation of digital RF Frequency Synthesizers 9

Eyediagram

Parameters:fch = 1.785 GHz;

fref

= 13 MHz;

n = 5 kHz;

Results:

E,rms = 1.41

E,max = 3.97

Specification:

E,rms,max = 5

E,abs,max = 20

-

7/29/2019 HDL based Simulation of digital RF Frequency Synthesizers

10/20

Chair of Integrated Analog Circuits

Andreas NeyerBMAS 2005

HDL based Simulation of digital RF Frequency Synthesizers 10

Power Spectral Density

-

7/29/2019 HDL based Simulation of digital RF Frequency Synthesizers

11/20

Chair of Integrated Analog Circuits

Andreas NeyerBMAS 2005

HDL based Simulation of digital RF Frequency Synthesizers 11

RMS Phase Error vs. Natural Frequency n

-

7/29/2019 HDL based Simulation of digital RF Frequency Synthesizers

12/20

Chair of Integrated Analog Circuits

Andreas NeyerBMAS 2005

HDL based Simulation of digital RF Frequency Synthesizers 12

Demonstration Example: Simulation Times

6 hmixed-signal simulator and

mixed-signal PLL

12 min.digital simulator

(event-triggered)

120 min.mixed-signal simulator withpure digital model

Simulation TimeSimulator

transient analysis of 2.2 ms on an Athlon 3200+ CPU

All-digital PLL

-

7/29/2019 HDL based Simulation of digital RF Frequency Synthesizers

13/20

Chair of Integrated Analog Circuits

Andreas NeyerBMAS 2005

HDL based Simulation of digital RF Frequency Synthesizers 13

Current RF Design Flow

system concept

engineering

tran-

sistor leveldesign

spectre

schematics periodic steady

state analysis

noise figures and

gain values

tools like MATLAB

system simulation

time domain

error rate

(BER)

design gap

closed by

spreadsheets,

containing

simulation

requirements

and

specifications

-

7/29/2019 HDL based Simulation of digital RF Frequency Synthesizers

14/20

Chair of Integrated Analog Circuits

Andreas NeyerBMAS 2005

HDL based Simulation of digital RF Frequency Synthesizers 14

Requirements in Modelling RF-Transceivers

Top-down design approach

Switchable cell views for simulation speed-up

Functional verification of the tape out database

Connectivity verification

Different cell views (baseband, transistor level etc.)

No manual interaction

Enhanced post processing

-

7/29/2019 HDL based Simulation of digital RF Frequency Synthesizers

15/20

Chair of Integrated Analog Circuits

Andreas NeyerBMAS 2005

HDL based Simulation of digital RF Frequency Synthesizers 15

Required Design Flow

single simulation

environment

same schematicson each signal domain

periodic steady

state analysis for

single blocks high performance

transient analysis for

functional verification

consistent databasesystem concept

engineering

transistor level

design

switchable signal domains

-

7/29/2019 HDL based Simulation of digital RF Frequency Synthesizers

16/20

Chair of Integrated Analog Circuits

Andreas NeyerBMAS 2005

HDL based Simulation of digital RF Frequency Synthesizers 16

Abstract Interface Modelling for RF Applications

Abstract data types

Use of new constructs like struct or record

Switchable cell views and consistent schematics

Same schematics and connections between basebandmodels and transistor level to ensure connectivitythroughout the design process

Companion Paper on this topic:

Mixed-Mode and Mixed-Domain Modelling and Verification of Radio Frequency

Subsystems for SoC-Applications, Poster by Stefan Joeres on BMAS 2005

-

7/29/2019 HDL based Simulation of digital RF Frequency Synthesizers

17/20

Chair of Integrated Analog Circuits

Andreas NeyerBMAS 2005

HDL based Simulation of digital RF Frequency Synthesizers 17

Proposed NCO Interface Descriptionusing a struct-/record-data type:

-

7/29/2019 HDL based Simulation of digital RF Frequency Synthesizers

18/20

Chair of Integrated Analog Circuits

Andreas NeyerBMAS 2005

HDL based Simulation of digital RF Frequency Synthesizers 18

TYPE complex_signal_t IS RECORDI, Q : real; -- in phase, quadrature phase

frequency : real; -- channel center frequency

[]

END RECORD;

TYPE nco_out_t IS RECORDfundamental : complex_signal_t; -- for baseband

[]

rf_out : bit; -- rf_output for loop feedback

END RECORD;

ENTITY nco ISPORT( fcw :IN bit_vector( fcw_length-1 downto 0);

nco_output :OUT nco_out_t);END ENTITY nco;

Proposed NCO Interface Declaration

typedef struct {real I, Q; // in phase, quadrature phase

real frequency; // channel center frequency

[]

} complex_signal_t;

typedef struct { // discrete time interfacecomplex_signal_t fundamental; // for baseband

[]

logic rf_out; // rf_output for loop feedback

} nco_out_t;

module nco (output nco_out_t nco_output,input [fcw_length-1:0] fcw);

using a struct-/record-datatype:

System-Verilog: VHDL(-AMS):

-

7/29/2019 HDL based Simulation of digital RF Frequency Synthesizers

19/20

Chair of Integrated Analog Circuits

Andreas NeyerBMAS 2005

HDL based Simulation of digital RF Frequency Synthesizers 19

HDL Languages on Schematic Level

Mixed-Signal-Simulators use Verilog-AMS or

Spice as top-level netlist format

Only analog nets and logic nets are available

No abstract data types supported on top-level

Abstract data types for interconnections required Supported by System-Verilog(-AMS) or VHDL-AMS

System-Verilog is coming soon

No AMS support in System-Verilog

-

7/29/2019 HDL based Simulation of digital RF Frequency Synthesizers

20/20

Chair of Integrated Analog Circuits

Andreas NeyerBMAS 2005

HDL based Simulation of digital RF Frequency Synthesizers 20

Summary

Proposing a RF interface modeling approach

Abstraction between connectivity and implementation level

Demonstrated by an All-digital PLL implementation

Future requirements for RF design tools

Better support and integration of HDLs in design flow

System-Verilog(-AMS) or VHDL-AMS as netlist format

Abstract signal types on schematic level

Functional and connectivity verification of the final tape outdatabase for RF applications