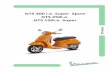

GTS NODE CARD FPGA BANK0 /BANK1 R. ISOCRATE 01/13 TST_TXN_3 TST_TXP_3 TST_RXN_3 TST_RXP_3 TST_TXN_2 TST_TXN_1 BTC_RSEL_1 BTC_TXF_2 E17 TC_MD2_2 1 TP7 1 TP6 J13 J12 J11 C13 B13 E13 D13 G13 F13 H12 H13 C12 F12 E12 E11 D11 G11 G12 E10 D10 F10 F11 G10 H11 D9 C9 G9 F9 B8 A8 D8 C8 E8 E9 F8 E7 D7 D6 C6 B3 A3 D12 H9 H10 C7 C10 IC27 2 1 R109 2 1 R108 2 1 R128 2 1 R127 2 1 C67 2 1 C93 2 1 C92 2 1 C94 2 1 C76 2 1 C68 J16 J15 J14 B14 C14 D14 E14 F14 G14 H14 H15 C15 D15 E15 F15 D16 E16 G15 G16 D17 F16 F17 H16 G17 C18 D18 F18 G18 A19 B19 C19 D19 E18 E19 F19 D20 E20 C21 D21 A24 B24 H18 H17 C20 C17 IC27 2 1 C95 2 1 C96 2 1 C111 2 1 C123 PHY_RX_DV PHY_TXD1 PHY_RXD3 PHY_RX_CLK TEMPERATURE_CLOCK TC_MD2_1 TC_MD2_0 PHY_SLW0 PHY_MDINT PHY_RX_ERR 33R 33R 33R 33R FPGA_CLK_CLEAN_N FPGA_CLK_CLEAN_P FPGA_CLK_REF_OE BTC_RSEL_0 TST_RXP_0 BTC_LOS_0 PHY_MDO PHY_TX_CLK NC BTC_RSEL_3 BTC_TXF_2 BTC_TXDIS_2 BTC_MD0_2 BTC_RSEL_2 BTC_TXDIS_1 BTC_TXF_0 BTC_TXDIS_0 BTC_MD0_0 BTC_LOS_3 TST_RXP_1 TST_RXN_0 TST_TXP_0 TST_TXN_0 BTC_MD1_0 TST_RXN_1 BTC_LOS_1 BTC_MD0_1 BTC_MD1_1 TST_RXP_2 TST_RXN_2 TST_TXP_1 TST_TXP_2 TEMPERATURE_DATA TC_MD2_3 PHY_SLW1 PHY_TX_ERR SMH_DIS SMH_ISEL SMH_LOCKED 16V 100NF 100NF 0.00 CONCEPTHDL15.1 X X 100NF 16V 16V 100NF 16V 16V 16V 100NF 16V 100NF 100NF PHY_TXD3 PHY_RXD1 PHY_TXD0 PHY_RXD2 PHY_CRS PHY_RESET PHY_COL PHY_TXD2 SMH_OSEL SDRAM_CLKX NC 100NF 16V 16V 100NF 100NF 16V PHY_TX_EN PHY_RXD0 PHY_MDC PAGE: DATE: ABBREV: TITLE: 1211 GENEVA 23 REF: ETUDE: 5 D B 1 D 8 8 7 7 6 6 5 4 4 3 3 2 2 1 C C B A A E E PCB: SYSTEM: REF: EDMS IT/CE SWITZERLAND DIV. DESSIN: VERSION: BANK 0 XC2VP7-FF672 IO_75P/GCLK4S_0 IO_75N/GCLK5P_0 IO_74P/GCLK6S_0 IO_74N/GCLK7P_0 IO_73P_0 IO_73N_0 IO_69P/VREF_0 IO_69N_0 IO_68P_0 IO_68N_0 IO_67P_0 IO_67N_0 IO_45P/VREF_0 IO_45_N_0 IO_44P_0 IO_44N_0 IO_43P_0 IO_43N_0 IO_39P_0 IO_39N_0 IO_38P_0 IO_38N_0 IO_37P_0 IO_37N_0 IO_09P_0 IO_09N_0 IO_08P_0 IO_08N_0 IO_07P_0 IO_07N_0 IO_06P_0 IO_06N_0 IO_05_0 IO_03P/VREF_0 IO_03N_0 IO_02P_0 IO_02N_0 IO_01P/VRN_0 IO_01N/VRP_0 J16_VCCO_0 J15_VCCO_0 J14_VCCO_0 H18_VCCO_0 H17_VCCO_0 C20_VCCO_0 C17_VCCO_0 BI OUT IN OUT IN IN OUT OUT DGND DGND DGND P2V5 DGND P3V3 DGND P3V3 DGND P2V5 P3V3 DGND P3V3 DGND P3V3 P3V3 P2V5 DGND P3V3 IN OUT IN OUT IN OUT OUT IN IN IN IN DGND IN IN IN IN OUT OUT OUT OUT OUT OUT P2V5 OUT OUT TP TP IN OUT IN OUT OUT OUT OUT OUT OUT OUT OUT OUT BANK 1 XC2VP7-FF672 J13_VCCO_1 J12_VCCO_1 J11_VCCO_1 H10_VCCO_1 C10_VCCO_1 H9_VCCO_1 C7_VCCO_1 IO_01P/VRN_1 IO_01N/VRP_1 IO_02P_1 IO_02N_1 IO_03P_1 IO_03N/VREF_1 IO_05_1 IO_06P_1 IO_06N_1 IO_07P_1 IO_07N_1 IO_08P_1 IO_08N_1 IO_09P_1 IO_09N/VREF_1 IO_37P_1 IO_37N_1 IO_38P_1 IO_38N_1 IO_39P_1 IO_39N_1 IO_43P_1 IO_43N_1 IO_44P_1 IO_44N_1 IO_45P_1 IO_45N/VREF_1 IO_67P_1 IO_67N_1 IO68P_1 IO_68N_1 IO_69P_1 IO_69N/VREF_1 IO_73P_1 IO_73N_1 IO_74P/GCLK0S_1 IO_74N/GCLK1P_1 IO_75P/GCLK2S_1 IO_75N/GCLK3P_1 OUT OUT OUT OUT P3V3 BI BI BI BI IN IN IN IN IN DGND IN IN IN IN P2V5 IN IN IN OUT DGND IN OUT OUT OUT IN IN P2V5

Welcome message from author

This document is posted to help you gain knowledge. Please leave a comment to let me know what you think about it! Share it to your friends and learn new things together.

Transcript

GTS NODE CARDFPGA BANK0 /BANK1

R. ISOCRATE

01/13

TST_TXN_3TST_TXP_3TST_RXN_3TST_RXP_3

TST_TXN_2

TST_TXN_1

BTC_RSEL_1

BTC_TXF_2E17

TC_MD2_2

1 TP7

1 TP6

J13J12J11

C13B13

E13D13

G13F13

H12H13

C12

F12E12

E11D11

G11G12

E10D10

F10F11

G10H11

D9C9

G9F9

B8A8

D8C8

E8E9

F8

E7D7

D6C6

B3A3

D12

H9

H10

C7

C10

IC27

21

R109

21

R108

21

R128

21

R127

21

C67 21

C9321

C9221

C9421

C7621

C68

J16J15J14

B14C14D14E14

F14G14

H14H15C15D15E15F15D16E16G15G16D17

F16F17H16G17C18D18F18G18A19B19C19D19E18E19F19D20E20C21D21A24B24

H18H17C20C17

IC27

21

C9521

C9621

C11121

C123

PHY_RX_DVPHY_TXD1PHY_RXD3PHY_RX_CLK

TEMPERATURE_CLOCKTC_MD2_1TC_MD2_0

PHY_SLW0PHY_MDINTPHY_RX_ERR

33R33R

33R33R

FPGA_CLK_CLEAN_NFPGA_CLK_CLEAN_P

FPGA_CLK_REF_OEBTC_RSEL_0

TST_RXP_0

BTC_LOS_0

PHY_MDO

PHY_TX_CLK

NC

BTC_RSEL_3BTC_TXF_2BTC_TXDIS_2

BTC_MD0_2BTC_RSEL_2

BTC_TXDIS_1

BTC_TXF_0BTC_TXDIS_0BTC_MD0_0

BTC_LOS_3

TST_RXP_1

TST_RXN_0

TST_TXP_0TST_TXN_0

BTC_MD1_0

TST_RXN_1BTC_LOS_1BTC_MD0_1BTC_MD1_1

TST_RXP_2TST_RXN_2TST_TXP_1

TST_TXP_2

TEMPERATURE_DATA

TC_MD2_3

PHY_SLW1

PHY_TX_ERRSMH_DISSMH_ISELSMH_LOCKED

16V100NF 100NF

0.00 CONCEPTHDL15.1XX

100NF16V16V

100NF16V16V16V

100NF16V100NF 100NF

PHY_TXD3PHY_RXD1

PHY_TXD0

PHY_RXD2

PHY_CRS

PHY_RESETPHY_COL

PHY_TXD2SMH_OSEL

SDRAM_CLKXNC

100NF16V 16V

100NF100NF16V

PHY_TX_EN

PHY_RXD0PHY_MDC

PAGE:

DATE:

ABBREV:

TITLE:

1211 GENEVA 23

REF:

ETUDE:

5

D

B

1

D

8

8 7

7 6

6 5

4

4 3

3 2

2

1

CC

B

AA

EE

PCB: SYSTEM:REF:EDMS

IT/C

E

SWITZERLAND

DIV.

DESSIN:

VERSION:

BANK 0XC2VP7-FF672

IO_75P/GCLK4S_0IO_75N/GCLK5P_0IO_74P/GCLK6S_0IO_74N/GCLK7P_0

IO_73P_0IO_73N_0

IO_69P/VREF_0IO_69N_0IO_68P_0IO_68N_0IO_67P_0IO_67N_0IO_45P/VREF_0IO_45_N_0IO_44P_0IO_44N_0IO_43P_0IO_43N_0

IO_39P_0IO_39N_0IO_38P_0IO_38N_0IO_37P_0IO_37N_0IO_09P_0IO_09N_0IO_08P_0IO_08N_0IO_07P_0IO_07N_0IO_06P_0IO_06N_0IO_05_0IO_03P/VREF_0IO_03N_0IO_02P_0IO_02N_0IO_01P/VRN_0IO_01N/VRP_0

J16_VCCO_0J15_VCCO_0J14_VCCO_0H18_VCCO_0H17_VCCO_0C20_VCCO_0C17_VCCO_0

BI

OUT

IN

OUT

IN

INOUT

OUT

DGND

DGND

DGND

P2V5

DGND

P3V3

DGND

P3V3

DGND

P2V5 P3V3

DGND

P3V3

DGND

P3V3P3V3P2V5

DGND

P3V3

IN

OUT

INOUT

IN

OUTOUT

ININ

ININ

DGND

ININ

ININ

OUTOUT

OUTOUT

OUTOUT

P2V5

OUTOUT

TP

TP

IN

OUT

IN

OUT

OUTOUT

OUT

OUT

OUT

OUT

OUT

OUT

BANK 1XC2VP7-FF672

J13_VCCO_1J12_VCCO_1J11_VCCO_1H10_VCCO_1C10_VCCO_1H9_VCCO_1C7_VCCO_1

IO_01P/VRN_1IO_01N/VRP_1IO_02P_1IO_02N_1IO_03P_1IO_03N/VREF_1IO_05_1IO_06P_1IO_06N_1IO_07P_1IO_07N_1IO_08P_1IO_08N_1IO_09P_1IO_09N/VREF_1IO_37P_1IO_37N_1IO_38P_1IO_38N_1IO_39P_1IO_39N_1

IO_43P_1IO_43N_1IO_44P_1IO_44N_1IO_45P_1IO_45N/VREF_1IO_67P_1IO_67N_1IO68P_1IO_68N_1IO_69P_1IO_69N/VREF_1

IO_73P_1IO_73N_1

IO_74P/GCLK0S_1IO_74N/GCLK1P_1IO_75P/GCLK2S_1IO_75N/GCLK3P_1

OUT

OUT

OUTOUT

P3V3

BIBI

BI

BI

IN

ININ

ININ

DGND

IN

IN

ININ

P2V5

IN

ININ

OUT

DGND

IN

OUT

OUT

OUT

IN

IN

P2V5

02/13

R. ISOCRATE

FPGA BANK2 /BANK3GTS NODE CARD

21

R130

21

R129

21

R110

21

R107

N9M9L9K8K2J8

N2N3N4N5N6N7M1M2M3M4M5M6N8M8L1L2L3L4L5L6M7L7L8K7K1J1K3K4K5K6J2J3J4J5J6J7H1H2H3H4H5H6G1F1G3G4G5G6E1E2E3E4D1D2C1C2B1A2D3C4

G2

IC27

21

C69 21

C78 21

C70 21

C80 21

C81 21

C82 21

C83 21

C84 21

C72 21

C73 21

C86

Y2V8U8U2T9R9P9

P3P2

P4

P7P6

R2R1

R4R3

R6R5

R8P8

T2T1

T4T3

T6T5

T7R7

U7T8

V1U1

U4

U6U5

V3V2

V5V4

V7V6

W2W1

W4W3

W6W5

AA1Y1

Y4Y3

Y6Y5

AB4AB3

AC2AC1

AD2AD1

AF2AE1

AD4AC3

AF3AE3

P5

U3

IC27

33R33R

33R33R

SDRAM_DQML_0

SDRAM_DQMH_1

SDRAM_DQMH_0

SDRAM_WESDRAM_CAS

SDRAM_DQML_1

SDRAM_CS

SDRAM_A1SDRAM_A0

SDRAM_A3SDRAM_BA1

SDRAM_A10

SDRAM_A2

SDRAM_DQ24

CR_CON2_023

BTC_TXF_1CR_CON2_011

RX_SEL1_3

SDRAM_DQ23SDRAM_DQ31SDRAM_DQ3

SDRAM_DQ27SDRAM_DQ30SDRAM_DQ9

SDRAM_DQ10

CR_CON2_022CR_CON2_024CR_CON2_010CR_CON2_012CR_CON2_033CR_CON2_035CR_CON2_021

CR_CON2_009

CR_CON1_005CR_CON1_003CR_CON1_017CR_CON1_015

NCNC

TX_SEL0_3RX_SEL1_2RX_SEL0_2TX_SEL1_2

RX_SEL0_3TX_SEL1_3

FPGA_CLK_RAW_P

CR_CON1_009

CR_CON1_023CR_CON1_035

FPGA_CLK_RAW_N

CR_CON2_036

CR_CON2_003

CR_CON2_017CR_CON2_018CR_CON2_015CR_CON2_016

100NF

USER_LED3

CR_CON1_016CR_CON1_004

16V

CR_CON1_024

CR_CON1_030CR_CON1_028

CR_CON1_018

CR_CON1_027CR_CON1_022CR_CON1_036CR_CON1_034

X

CR_CON2_004CR_CON2_006CR_CON2_005CR_CON2_034

CR_CON2_027CR_CON2_029

CR_CON1_006

100NF16V

100NF16V100NF

16V100NF

16V16V100NF100NF

16V16V100NF 100NF

16V100NF 100NF

SDRAM_DQ8

SDRAM_DQ0

SDRAM_DQ20SDRAM_DQ6

X

16V

X

16V

CR_CON1_029

CR_CON1_012

CR_CON1_033CR_CON1_021CR_CON1_010

0.00X

SDRAM_CKE

SDRAM_A11SDRAM_A12

SDRAM_DQ29SDRAM_DQ26

SDRAM_DQ17

SDRAM_A4

SDRAM_DQ1

SDRAM_DQ21

SDRAM_DQ28

SDRAM_DQ11

SDRAM_RASSDRAM_DQ25

SDRAM_BA0

CR_CON1_011

SDRAM_DQ16SDRAM_DQ4SDRAM_DQ5SDRAM_DQ15

SDRAM_DQ13SDRAM_DQ2SDRAM_DQ12

SDRAM_DQ22SDRAM_DQ19

SDRAM_A6

SDRAM_CLK

SDRAM_DQ14SDRAM_DQ7SDRAM_DQ18

SDRAM_A9SDRAM_A8SDRAM_A7

SDRAM_A5

PAGE:

DATE:

ABBREV:

TITLE:

1211 GENEVA 23

REF:

ETUDE:

5

D

B

1

D

8

8 7

7 6

6 5

4

4 3

3 2

2

1

CC

B

AA

EE

PCB: SYSTEM:REF:EDMS

IT/C

E

SWITZERLAND

DIV.

DESSIN:

VERSION:

BIBIBI

BIBI

BI

BI

BI

P3V3

DGND

P2V5

DGND

P2V5

BANK 2XC2VP7-FF672

N9_VCCO_2M9_VCCO_2L9_VCCO_2K8_VCCO_2K2_VCCO_2J8_VCCO_2G2_VCCO_2

IO_90P_2IO_90N_2IO_89P_2IO_89N_2IO_88P_2IO_88N/VREF_2IO_87P_2IO_87N_2IO_86P_2IO_86N_2IO_85P_2IO_85N_2IO_60P_2IO_60N_2IO_59P_2IO_59N_2IO_58P_2IO_58N_2IO_57P_2IO_57N_2IO_56P_2IO_56N_2IO_55P_2IO_55N_2IO_54P_2IO_54N_2IO_53P_2IO_53N_2IO_52P_2IO_52N/VREF_2IO_51P_2IO_51N_2IO_50P_2IO_50N_2IO_49P_2IO_49N_2IO_48P_2IO_48N_2IO_47P_2IO_47N_2IO_46P_2IO_46N/VREF_2IO_45P_2IO_45N_2IO_44P_2IO_44N_2IO_43P_2IO_43N_2IO_06P_2IO_06N_2IO_05P_2IO_05N_2IO_04P_2IO_04N/VREF_2IO_03P_2IO_03N_2IO_02P_2IO_02N_2IO_01P/VRN_2IO_01N/VRP_2

P3V3

P3V3P3V3P3V3P3V3P3V3

DGNDDGND DGND DGND

P3V3

DGND DGND DGNDDGND

P2V5

IN

OUTOUTOUTOUT

OUT

OUT

OUTOUT

BIBI

BI

BI

P2V5

BI

BIBI

BIBIBI

BIBIBIBI

DGND

BIBIBI

BIBIBIBIBI

BI

DGND

BANK 3XC2VP7-FF672

Y2_VCCO_3V8_VCCO_3U8_VCCO_3U2_VCCO_3T9_VCCO_3R9_VCCO_3P9_VCCO_3

IO_01P/VRN_3IO_01N/VRP_3IO_02P_3IO_02N_3IO_03P_3IO_03N/VREF_3IO_04P_3IO_04N_3IO_05P_3IO_05N_3IO_06P_3IO_06N_3IO_43P_3IO_43N_3IO_44P_3IO_44N_3IO_45P_3IO_45N/VREF_3IO_46P_3IO_46N_3IO_47P_3IO_47N_3IO_48P_3IO_48N_3IO_49P_3IO_49N_3IO_50P_3IO_50N_3IO_51P_3IO_51N/VREF_3IO_52P_3IO_52N_3IO_53P_3IO53N_3IO_54P_3IO_54N_3IO_55P_3IO_55N_3IO_56P_3IO_56N_3IO_57P_3IO_57N_3IO_58P_3IO_58N_3IO_59P_3IO_59N_3IO_60P_3IO_60N_3IO_85P_3IO_85N_3IO_86P_3IO_86N_3IO_87P_3IO_87N/VREF_3IO_88P_3IO_88N_3IO89P_3IO_89N_3IO_90P_3IO_90N_3

BIBIBI

OUTOUT

OUT

OUTOUT

OUTOUT

P2V5

OUTOUTOUT

OUT

OUTOUT

OUT

OUTOUT

OUTOUTOUTOUT

BI

BIBI

BIBI

BI

BI

BIBIBIBI

BIBIBI

P2V5

BIBIBI

BIBIBIBI

BIBI

DGND

BIBIBIBIBIBI

BIBI

BIBI

BIBIBIBIBIBIBI

BIBI

BI

OUTOUT

BI

P2V5

GTS NODE CARD

THESE TWO DECOUPLING CAPS SHOULDBE PLACED CLOSE TOGHETHER (EVERYWERE)

03/13

R. ISOCRATE

FPGA BANK4 /BANK5

560PF INSTEAD OF 1NF

21

C109

21

C110

21

R52

21

R131

21

R56

21

R132

21

R55 21

R51

21

R54

21

R53

1TP14

1TP13

21

R47

21

R46

21

R57

21

R58

W18W17V16V15V14

AD21

AD14AE14

AB14AC14

Y14AA14

W15W14

AC15AD15

AA15AB15

AB16AC16

Y16Y15

AB17AC17

AA17AA16

Y17W16

AC18AD18

Y18AA18

AE19AF19

AC19AD19

AB19AB18

Y19

AA20AA19

AB20AC20

AC21

AD20AD17

IC27

21

C88 21

C101 21

C103 21

C89 21

C90 21

C102

21

C104 21

C105 21

C122 21

C108

W9

W10V13V12V11

AA9

AB7AD6

AB9

AE13AD13AC13AB13

AA13Y13

W13W12

AD12AC12AB12AA12AC11AB11

Y12Y11

AC10AB10

AA11AA10

W11Y10AD9AC9

Y9AF8AE8AD8AC8

AB8Y8

AA8AA7AC7

AC6

AD7

AD10

IC27

33R33R

33R33R

CR_CON1_065

CR_CON1_063

CLKREF_NCLKREF_P

CR_CON2_065CR_CON2_063

CR_CON2_060CR_CON2_058CR_CON2_066CR_CON2_064CR_CON2_070

CR_CON2_071CR_CON2_069

CR_CON2_077

CR_CON2_078

TX_SEL0_0TX_SEL1_0

CR_CON1_078CR_CON1_076

CR_CON1_065

CR_CON1_071CR_CON1_069

CR_CON1_077CR_CON1_075

TX_SEL0_2RX_SEL1_1RX_SEL0_1TX_SEL1_1TX_SEL0_1RX_SEL1_0RX_SEL0_0

CR_CON2_076

CR_CON2_075

CR_CON2_072

CR_CON1_063

CR_CON1_070CR_CON1_072

CR_CON1_064CR_CON1_066CR_CON2_112_FPGA_INIT

CARRIER_CLK_NCARRIER_CLK_P

CR_CON2_059

CR_CON2_052CR_CON2_054

CR_CON2_051CR_CON2_053

CR_CON2_045CR_CON2_047

CR_CON2_046CR_CON2_048

CR_CON2_040

CR_CON2_041

CR_CON1_047CR_CON1_045

CR_CON2_057

CR_CON1_052CR_CON1_054

CR_CON1_057CR_CON1_059

CR_CON1_046CR_CON1_048CR_CON1_051CR_CON1_053

CR_CON2_039

FPGA_DIN

CR_CON1_039

CR_CON1_060

16V100NF16V

CR_CON1_041

NC

CR_CON2_042

CR_CON1_040CR_CON1_042CR_CON1_058

16V16V100NF 100NF

16V100NF 100NF

16V

X X0.00 CONCEPTHDL15.1

16V100NF100NF

16V100NF16V

100NF16V

100NF

1.3K

820R

1.3K

82R

130R130R

82R820R50V1.0NF

1.0NF50V

PAGE:

DATE:

ABBREV:

TITLE:

1211 GENEVA 23

REF:

ETUDE:

5

D

B

1

D

8

8 7

7 6

6 5

4

4 3

3 2

2

1

CC

B

AA

EE

PCB: SYSTEM:REF:EDMS

IT/C

E

SWITZERLAND

DIV.

DESSIN:

VERSION:

BIBI

BIBI

BIBI

BIBI

BIBI

IN

IN

BIBI

BIBI

BIBI

BIBI

BIBI

BIBI

BIBI

BIBIBIBI

BIBI

BIBI

BIBIBIBI

BI

BI

BIBI

ININ

DGND

P2V5DGND

P2V5

P2V5

BANK 5XC2VP7-FF672

AD20_VCCO_5AD17_VCCO_5W18_VCCO_5W17_VCCO_5V16_VCCO_5V15_VCCO_5V14_VCCO_5

IO_01P/CSB_5IO_O1N/RDWRB_5IO_02P/D7_5IO_02N/D6_5IO_03P/D5_5IO_03N/D4_5IO_05_5IO_06P/VRN_5IO_06N/VRP_5IO_07P_5IO_07N/VREF_5IO_08P_5IO_08N_5IO_09P_5IO_09N/VREF_5IO_37P_5IO_37N_5IO_38P_5IO_38N_5IO_39P_5IO_39N_5

IO_43P_5IO_43N_5IO_44P_5IO_44N_5IO_45P_5IO_45N/VREF_5IO_67P_5IO_67N_5IO_68P_5IO_68N_5IO_69P_5IO_69_N/VREF_5

IO_73P_5IO_73N_5

IO_74P/GCLK4P_5IO_74N/GCLK5S_5IO_75P/GCLK6P_5IO_75N/GCLK7S_5

P2V5

DGND

P2V5

DGND

P2V5 P2V5

DGND DGND

P2V5

DGND

P2V5

DGND

P2V5

DGND

P2V5

DGND

BANK 4XC2VP7-FF672

IO_75P/GCLK0P_4IO_75N/GCLK1S_4IO_74P/GCLK2P_4IO_74N/GCLK3S_4

IO_73P_4IO_73N_4

IO_69P/VREF_4IO_69N_4IO_68P_4IO_68N_4IO_67P_4IO_67N_4IO_45P/VREF_4IO_45N_4IO_44P_4IO_44N_4IO_43P_4IO_43N_4

IO_39P_4IO_39N_4IO_38P_4IO_38N_4IO_37P_4IO_37N_4IO_O9P/VREF_4IO_09N_4IO_08P_4IO_08N_4IO_07P/VREF_4IO_07N_4IO_L06P/VRN_4IO_06N/VRP_4IO_05_4IO_03P/D3_4IO_03N/D2_4IO_02P/D1_4IO_O2N/D0_4IO_O1P_/INITB_4IO_01N/DOUT_4

AD10_VCCO_4W10_VCCO_4V13_VCCO_4V12_VCCO_4V11_VCCO_4AD7_VCCO_4W9_VCCO_4

P2V5 P2V5

DGND

OUTOUTOUTOUTOUTOUTOUT

OUTOUT

DGND DGND DGND

P3V3 P3V3

DGND DGND

P3V3 P3V3

TP

P2V5

TP

BIBI

BIBIBIBIBIBI

BIBIBIBI

BIBI

BIBI

04/13

R. ISOCRATE

FPGA BANK6 /BANK7GTS NODE CARD

1TP21

1TP20

21

R25

21

R26

21

R135

21

R136

21

C117 21

C118 21

C120 21

C128 21

C129 21

C115 21

C116 21

C113 21

C125 21

C126

Y25V19U25U19T18R18P18

P24P25

P22P23

P20P21

R25R26

R23R24

R21R22

R19P19

T25T26

T23T24

T21T22

T20R20

U20T19

V26U26

U23U24

U21U22

V24V25

V22V23

V20V21

W25W26

W23W24

W21W22

AA26Y26

Y23Y24

Y21Y22

AB23AB24

AC25AC26

AD25AD26

AE26AF25

AC24

AF24AE24AD23

IC27

N18M18L18K25K19J19

N25N24N23N22N21N20M26M25M24M23M22M21N19M19L26L25L24L23L22L21M20L20L19K20K26J26K24K23K22K21J25J24J23J22J21J20H26H25H24H23H22H21G26F26G24G23G22G21E26E25E24E23D26D25C26C25B26A25D24C23

G25

IC27

33R33R

33R33R

CR_CON2_094

CR_CON2_093CR_CON2_095

CR_CON1_112

CR_CON1_089

CR_CON1_082

CR_CON1_107

CR_CON1_108CR_CON1_104

CR_CON1_084

040216V100NF 100NF

16V0402

100NF16V0402

100NF16V0402

100NF16V0402

100NF040216V

040216V100NF

BOOT_A22BOOT_CE1BOOT_A21BOOT_A20BOOT_A19BOOT_A18BOOT_A16BOOT_A15BOOT_A14BOOT_A13BOOT_A12BOOT_CE0BOOT_A17BOOT_RPBOOT_A11BOOT_A10BOOT_A9BOOT_A8

BOOT_A6

BOOT_A5BOOT_A4

BOOT_A1BOOT_A2BOOT_A23BOOT_CE2BOOT_DQ9

BOOT_OE

BOOT_A0BOOT_DQ0BOOT_DQ8BOOT_DQ1

BOOT_A7

BOOT_DQ11BOOT_DQ4BOOT_DQ10

CR_CON2_088

CR_CON2_087

EEPROM_Q

BOOT_DQ2

EEPROM_WRITE

16V100NF

BOOT_WEBOOT_A24

040216V100NF0402

CR_CON2_109

EEPROM_HOLD

CR_CON1_105CR_CON1_103

EEPROM_SEL

CONCEPTHDL15.1XX

DLY_0DLY_1

DLY_8DLY_9DLY_10

DLY_7

DLY_2DLY_3DLY_4DLY_5DLY_6

CR_CON1_090

BOOT_DQ3

BOOT_DQ6BOOT_DQ13BOOT_DQ5BOOT_DQ12BOOT_DQ7BOOT_DQ14

CR_CON1_083CR_CON1_081

CR_CON2_083CR_CON2_081

CR_CON2_103

CR_CON1_106

CR_CON2_090

BOOT_STSBOOT_DQ15

100NF

0.00

040216V

CR_CON1_109

CR_CON1_087

CR_CON1_088

CR_CON1_110

SMDSMD

USER_LED2USER_LED1USER_LED0

EEPROM_CLK

EEPROM_DATA

BOOT_A3

BOOT_BYTE

CR_CON2_089

CR_CON2_105

CR_CON1_096

CR_CON2_096

CR_CON1_095CR_CON1_093

CR_CON1_111CR_CON1_094

CR_CON2_107CR_CON2_082CR_CON2_084

BTC_MD1_2BTC_LOS_2

BTC_MD0_3

BTC_MD1_3

BTC_TXDIS_3BTC_TXF_3CR_CON2_100

PAGE:

DATE:

ABBREV:

TITLE:

1211 GENEVA 23

REF:

ETUDE:

5

D

B

1

D

8

8 7

7 6

6 5

4

4 3

3 2

2

1

CC

B

AA

EE

PCB: SYSTEM:REF:EDMS

IT/C

E

SWITZERLAND

DIV.

DESSIN:

VERSION:

OUT

BIBIBIBI

BIBI

P3V3

BI

BIBI

BIBI

BIBI

BIBI

BI

BIBI

BI

BIBI

BI

BI

BIBI

BI

BIBIBI

BIBIBIBI

BIBI

BI

BI

BIBI

P3V3

DGND

DGND

P2V5

P3V3

P2V5

DGND

P2V5

DGND

P2V5 P2V5

DGND DGND

P2V5

DGND

P2V5

DGND

P3V3

DGND

XC2VP7-FF672BANK 6

Y25_VCCO_6V19_VCCO_6U25_VCCO_6U19_VCCO_6T18_VCCO_6R18_VCCO_6P18_VCCO_6

IO_90N_6IO_90P_6IO_89N_6IO_89P_6IO_88N_6IO_88P_6IO_87N/VREF_6IO_87P_6IO_86N_6IO_86P_6IO_85N_6IO_85P_6IO_60N_6IO_60P_6IO_59N_6IO_59P_6IO_58N_6IO_58P_6IO_57N/VREF_6IO_57P_6IO_56N_6IO_56P_6IO_55N_6IO_55P_6IO_54N_6IO_54P_6IO_53N_6IO_53P_6IO_52N_6IO_52P_6IO_51N_6IO_51P_6IO_50N_6IO_50P_6IO_49N_6IO_49P_6IO_48N_6IO_48P_6IO_47N_6IO_47P_6IO_46N_6IO_46P_6IO_45N/VREF_6IO_45P_6IO_44N_6IO_44P_6IO_43N_6IO_43P_6IO_06N_6IO_06P_6IO_05N_6IO_05P_6IO_04N_6IO_04P_6IO_03N/VREF_6IO_03P_6IO_02N_6IO02P_6IO_01N/VRP_6IO_01P/VRN_6

INOUT

IN

OUT

OUTIN

TP

TP

OUTOUTOUT

P3V3

OUTOUTOUTOUTOUTOUTOUTOUT

OUTOUT

DGND

INBI

BI

OUT

BIOUT

BI

BI

OUTOUTOUTOUT

OUTOUTOUTOUT

P3V3

BIBIBI

BIBIBI

DGND

BIBIBIBIBIBI

OUT

OUT

OUT

IN

OUT

OUTOUTOUT

OUT

DGND

OUT

OUTOUTOUTOUTOUTOUTOUTOUTOUTOUTOUTOUTOUTOUTOUT

OUTOUT

P3V3

BANK 7XC2VP7-FF672

N18_VCCO_7M18_VCCO_7L18_VCCO_7K25_VCCO_7K19_VCCO_7J19_VCCO_7G25_VCCO_7

IO_01N/VRP_7IO_01P/VRN_7IO_02N_7IO_02P_7IO_03N_7IO_03P_7IO_04N/VREF_7IO_04P_7IO_05N_7IO_05P_7IO_06N_7IO_06P_7IO_43N_7IO_43P_7IO_44N_7IO_44P_7IO_45N_7IO_45P_7IO_46N/VREF_7IO_46P_7IO_47N_7IO_47P_7IO_48N_7IO_48P_7IO_49N_7IO_49P_7IO_50N_7IO_50P_7IO_51N_7IO_51P_7IO_52N/VREF_7IO_52P_7IO_53N_7IO_53P_7IO_54N_7IO_54P_7IO_55N_7IO_55P_7IO_56N_7IO_56P_7IO_57N_7IO_57P_7IO_58N/VREF_7IO_58P_7IO_59N_7IO_59P_7IO_60N_7IO_60P_7IO_85N_7IO_85P_7IO_86N_7IO_86P_7IO_87N_7IO_87P_7IO_88N/VREF_7IO_88P_7IO_89N_7IO_89P_7IO_90N_7IO_90P_7

GUARDS (SEE MAXIM MAX1617A DATA SHEET)THESE TRACES SHOULD BE ROUTED INSIDE

05/13

R. ISOCRATE

FPGA MISCELLANEUSGTS NODE CARD

12

LD5

2

1

3

T2

21

R12

21

R13

1TP121TP11

21

C17721

R22

2

15

12

14

3

4

11610

IC42

1

R138

21

R133

21

R59

21

R61

21

R134

21

R60

21

R62

21

R45

Y7

Y20

W8

W19

E6

V9

V18V17V10

U9

U18U17U16U15U14U13U12

U11

U10

F7

H7H20

G8

T17

T16T15T14T13T12T11

T10

D5

R17R16R15R14R13R12R11R10

AC5

D22

P26

P1

P17P16P15P14P13P12P11P10

N26

N1

N17N16N15N14N13N12N11N10

AB21W20

AC22

M17M16M15M14M13M12M11M10

L17

L16L15L14L13L12L11

L10

K9

K18

K17

K16

K15K14K13K12

K11

K10

J9

J18J17J10

E21

H8

H19

G7

G20

F6

F21

E5

E22

F20G19

AB6

D4

D23

W7

C3

C24

B2

B25

AF14AF13

AE2

AE25

AD3

AD24

AC4

AC23

AB5

AB22

AA6

AA21

A14A13

IC27

21

C100

21

C79

21

C119 21

C114

21

C121 21

C112

21

C10621

C91 21

C85

21

C9721

C8721

C77

21

C74 21

C127 21

C107

21

C66 21

C124 21

C130 21

C71

220R

330R

FPGA_DONE

FPGA_TDICR_CON2_104_TCKCR_CON2_106_TMS

100NF16V 16V

100NF

CR_CON2_111_FPGA_PROGRAMFPGA_CCLKFPGA_DONE

100NF16V

TEMPERATURE_DATA

KPA-2106I196

BSS138

CR_CON2_110_TDO

4.7K5%

100NF

16V

4.7K

SMDSMD

4.7K

4.7K

5%

4.7K4.7K4.7K5%

100NF16V

16V100NF

16V100NF

16V

100NF

16V

100NF16V

16V

16V100NF

100NF16V

100NF16V

16V100NF 100NF

16V

16V

X X CONCEPTHDL15.1X0.00X

4.7K5%

4.7K5%

5% 5%

100NF

16V

100NF

NC

100NF

16V

100NF16V100NF

TEMPERATURE_CLOCK

100NF

5%

PAGE:

DATE:

ABBREV:

TITLE:

1211 GENEVA 23

REF:

ETUDE:

5

D

B

1

D

8

8 7

7 6

6 5

4

4 3

3 2

2

1

CC

B

AA

EE

PCB: SYSTEM:REF:EDMS

IT/C

E

SWITZERLAND

DIV.

DESSIN:

VERSION:

P1V5P1V5

DGNDDGND DGND

DGNDDGND DGND

DGND

P2V5

DGND

P2V5

DGND

P2V5

DGND

P2V5

DGND

P2V5

DGND

P2V5

DGND

P2V5

DGND

P1V5

P2V5

DGND

P2V5 P3V3

TPTP

P2V5OUT

IN

P3V3 P3V3

DGND

DGND DGND

P3V3

MAX1617A

VCC

SMBDATAALERT*

SMBCLK

STBY*

ADD1ADD0

DXN

DXP

GND<1-0>

OUTIN

IN

OUTINININ

DGND

DGNDDGNDDGND

P2V5P2V5P2V5

P2V5

MISCXC2VP7-FF672

K16_VCCINT

W19_VCCINTV18_VCCINTV17_VCCINTV10_VCCINTU18_VCCINTU16_VCCINTU11_VCCINTT17_VCCINTT10_VCCINTL17_VCCINTL10_VCCINTK18_VCCINT

K11_VCCINTJ18_VCCINTJ17_VCCINTJ10_VCCINTH19_VCCINTW8_VCCINTV9_VCCINTU9_VCCINTK9_VCCINTJ9_VCCINTH8_VCCINT

AF14_VCCAUXAF13_VCCAUXAE25_VCCAUXP26_VCCAUXN26_VCCAUXB25_VCCAUXAE2_VCCAUXA14_VCCAUXA13_VCCAUXP1_VCCAUXN1_VCCAUXB2_VCCAUX

AD24_GNDAC23_GNDAB22_GNDAA21_GND

Y20_GNDU17_GNDU15_GNDU14_GNDU13_GNDU12_GNDU10_GNDT16_GNDT15_GNDT14_GNDT13_GNDT12_GNDT11_GNDR17_GNDR16_GNDR15_GNDR14_GNDR13_GNDR12_GNDR11_GNDR10_GNDP17_GNDP16_GNDP15_GNDP14_GNDP13_GNDP12_GNDP11_GNDP10_GNDN17_GNDN16_GNDN15_GNDN14_GNDN13_GNDN12_GNDN11_GNDN10_GNDM17_GNDM16_GNDM15_GNDM14_GNDM13_GNDM12_GNDM11_GNDM10_GNDL16_GNDL15_GNDL14_GNDL13_GNDL12_GNDL11_GNDK17_GNDK15_GNDK14_GNDK13_GNDK12_GNDK10_GNDG20_GNDF21_GNDE22_GNDD23_GNDC24_GNDAD3_GNDAC4_GNDAB5_GNDAA6_GND

Y7_GNDG7_GNDF6_GNDE5_GNDD4_GNDC3_GND

TDOTDITCKTMS

CCLKDONEPROGB

MODE2MODE1MODE0

VBATTRSVDHSWAP_ENPWRDWNBDXNDXP

DGND

P1V5

DGND

P1V5

DGND

P1V5

DGND

P1V5

DGND

P1V5

DGND

P1V5

P1V5P1V5P1V5

P1V5

THES TWO (X8) 0R RESISTORS SHOULDBE PLACED CLOSE TOGHETHER (EVERYWERE)

06/13

R. ISOCRATE

FPGA MGT BOTTOM AND TOPGTS NODE CARD

MURATA BLM18AG102SN1 (EIA 0603 SIZE)

21

C46

21

C47

21

C48

21

C49

21

C50

21

C51

21

C52

21

C53

21

C54

21

C55

21

C56

21

C57

21

C58

21

C59

21

C60

21

C61

21 L1421 L1321 L1221 L11

21 L1821 L1721 L1621 L15

21 L2221 L2121 L2021 L19

21 L23

21 L24

21 L25

21 L26

AE23

AE18

AE12

AE7

AE21

AE16

AE10

AE5

AF22

AF17

AF11

AF6

AF23

AF18

AF12

AF7

AF21

AF16

AF10

AF5

AF20

AF15

AF9

AF4

AE22

AE17

AE11

AE6

AE20

AE15

AE9

AE4

AD22

AD16

AD11

AD5

IC27

B7

B12

B18

B23

B5

B10

B16

B21

A6

A11

A17

A22

A7

A12

A18

A23

A5

A10

A16

A21

A4

A9

A15

A20

B6

B11

B17

B22

B4

B9

B15

B20

C5

C11

C16

C22

IC27

MGT_RXDN_3MGT_RXDP_3

MGT_TXDP_3MGT_TXDN_3

MGT_RXDN_2MGT_RXDP_2

MGT_TXDP_2MGT_TXDN_2

MGT_RXDN_1MGT_RXDP_1

MGT_TXDP_1MGT_TXDN_1

MGT_RXDN_0MGT_RXDP_0

MGT_TXDP_0MGT_TXDN_0

200NF

VTTRX_MGT

1000ZILBB_0603

I263200NF

I262200NF

I261200NF200NF

200NFI267I266

200NFI265200NF

I264

I271200NF

I270200NF

I269200NF

I268200NF

I275200NF

I274200NF

I273200NF

I272200NF

ILBB_0603

ILBB_06031000Z

VTTTX_MGT

1000Z1000Z1000Z

VTTRX_MGT

0.00X X CONCEPTHDL15.1

VTTTX_MGT

ILBB_0603

VTTTX_MGT

ILBB_0603

ILBB_0603ILBB_0603

ILBB_06031000ZILBB_06031000Z

1000Z ILBB_06031000Z ILBB_0603

1000Z ILBB_06031000Z1000Z ILBB_0603

ILBB_0603

NCNC

NC

NCNC

NCNC

NC

NC

NC

NCNC

NC

NC

NC

NC 1000Z

1000Z

VTTRX_MGT

1000Z

VTTTX_MGT

VTTRX_MGT

ILBB_0603

ILBB_06031000Z

PAGE:

DATE:

ABBREV:

TITLE:

1211 GENEVA 23

REF:

ETUDE:

5

D

B

1

D

8

8 7

7 6

6 5

4

4 3

3 2

2

1

CC

B

AA

EE

PCB: SYSTEM:REF:EDMS

IT/C

E

SWITZERLAND

DIV.

DESSIN:

VERSION:

P2V5A

AGND

P2V5A

P2V5A

P2V5AP2V5A

OUTOUT

ININ

OUTOUT

ININ

OUTOUT

ININ

OUTOUT

ININ

AGND AGND AGND AGND

AGND AGND

MGT TOPXC2VP7-FF672

TX_N_9TX_P_9

RX_P_9RX_N_9

AGND_9

VTT_TX_9

AVCCAUX_TX_9

VTT_RX_9

AVCCAUX_RX_9

TX_N_7TX_P_7

RX_P_7RX_N_7

AGND_7

VTT_TX_7

AVCCAUX_TX_7

VTT_RX_7

AVCCAUX_RX_7

TX_N_6TX_P_6

RX_P_6RX_N_6

AGND_6

VTT_TX_6

AVCCAUX_TX_6

VTT_RX_6

AVCCAUX_RX_6

TX_P_4TX_N_4

RX_P_4RX_N_4

AGND_4

AVCCAUX_RX_4

VTT_RX_4

VTT_TX_4

AVCCAUX_TX_4

AGND AGND

AGND AGND AGND AGND

AGNDAGNDAGNDAGND

AGND

P2V5AVCC_BARVCC_BARAGND

P2V5AVCC_BARVCC_BAR

AGND

P2V5AVCC_BARVCC_BAR

VCC_BAR VCC_BAR

AGND

AGND

AGND

AGND

XC2VP7-FF672MGT BOTTOM

TX_N_21TX_P_21

RX_P_21RX_N_21

AGND_21

VTT_TX_21

AVCCAUX_TX_21

VTT_RX_21

AVCCAUX_RX_21

TX_N_19TX_P_19

RX_P_19RX_N_19

AGND_19

VTT_TX_19

AVCCAUX_TX_19

VTT_RX_19

AVCCAUX_RX_19

TX_N_18TX_P_18

RX_P_18RX_N_18

AGND_18

VTT_TX_18

AVCCAUX_TX_18

VTT_RX_18

AVCCAUX_RX_18

AGND_16

VTT_TX_16

AVCCAUX_TX_16

VTT_RX_16

AVCCAUX_RX_16

TX_N_16TX_P_16

RX_P_16RX_N_16

GTS NODE CARDSFP TRANSCEIVERS

R. ISOCRATE

07/13

98765

3

20

2

1918171615141312

10

1

M1

9876543

20

2

1918171615141312

1110

1

M3

9876543

20

2

1918171615141312

1110

1

M4

9876543

20

2

1918171615141312

1110

1

M2

21L6

21

L7

21L2

21

L3

21

C22

21

C21

21

C19

21

C20

16

15

231819

1312

7

456

8

J5

63

RZ10

81

RZ10

63

RZ9

21

C10

21

C9

21

C7

21

C8

81

RZ9

63

RZ14

81

RZ14

63

RZ13

81

RZ13

16

15

231819

1312

7

456

8

J3

54

RZ10

72

RZ10

54

RZ9

72

RZ9

54

RZ14

72

RZ14

54

RZ13

72

RZ13

81

RZ15

63

RZ15

81

RZ16

63

RZ16

81

RZ11

63

RZ11

81

RZ12

16

15

231819

1312

7

456

8

J6

21

C24

21

C23

63

RZ12

21

C25

21

L9

21

C2621

L8

21

L5

54

RZ12

72

RZ12

54

RZ11

72

RZ11

54

RZ16

72

RZ16

54

RZ15

72

RZ15

16

15

231819

1312

7

456

8

J4

21L4 2

1

C16

21

C15

21

C13

21

C14

TRC_RXP_0

TC_TXF_0

TRC_RXN_0

GND=AGND100NF 10UF 100NF

10K

10K

TRC_RXP_2TC_LOS_2

TC_TXF_2

10UF

TRC_TXN_0TRC_TXP_0

TC_TXDIS_0TC_RSEL_0

TRC_RXN_1

TRC_RXP_3TRC_RXN_3

TRC_TXN_3TRC_TXP_3

TRC_RXN_2

TRC_TXN_2TRC_TXP_2

TRC_RXP_1

TRC_TXN_1TRC_TXP_1

I217

TC_MD0_0TC_MD1_0

TC_MD0_1TC_RSEL_1TC_TXDIS_1

1UH

10K

10K

10K

NC

GND=AGND GND=AGND

GND=AGND

TC_MD2_2

100NF

10UF

10UF10UF

10UF16V

TC_LOS_1

100NF

1UH

100NF

TC_TXF_3

TC_LOS_3

100NF16V

1UH16V

TC_TXDIS_3TC_RSEL_3

100NF

10K

16V

1UH

1UH16V

10UF100NF16V10UF16V

TC_MD1_2TC_MD0_2TC_RSEL_2TC_TXDIS_2

CONCEPTHDL15.1X 0.00 X

TC_TXF_1

1UH

TC_MD2_0

10K

10K

10K

10K

10K

10K

10K

10K

10K

10K

NC

10K

10K

10K

10K

10K

10K

10K

10K

10K

NC

10K

10K

TC_MD0_3TC_MD1_3TC_MD2_3

10K

16V

TC_MD2_1

10K

10K

10K

NC

TC_MD1_1

TC_LOS_0

1UH

1UH

10K

PAGE:

DATE:

ABBREV:

TITLE:

1211 GENEVA 23

REF:

ETUDE:

5

D

B

1

D

8

8 7

7 6

6 5

4

4 3

3 2

2

1

CC

B

AA

EE

PCB: SYSTEM:REF:EDMS

IT/C

E

SWITZERLAND

DIV.

DESSIN:

VERSION:

+

AGND

OUT

BI

IN

IN

P3V3

ININ

P3V3

OUT

IN

BI

IN

OUT

OUT

P3V3

P3V3 P3V3 P3V3 P3V3 P3V3 P3V3 P3V3 P3V3

1367073_1TYCO

VCCR

TD-TD+TX_DISVCCT

RATEMOD_DEF0MOD_DEF1MOD_DEF2

LOS

FAULTTX_

RD+RD-

SFP CONNECTOR

OUTOUT

ININ

P3V3

AGND

+

AGND AGND

+

AGND

2

HOLE TYPE 3

2

SFP_CAGE_18HOLE

2 HOLE TYPE 2

pads and via

22

2

optional

plating

thru holes

3

33333

333

22

ground

are chassis2

AGND AGND

AGNDAGND

optional

plating

thru holes

ground

are chassis

pads and via

3

33333

2

333

2

2222

2

22

22

HOLE TYPE 3

SFP_CAGE_20HOLE

HOLE TYPE 2

optional

plating

thru holes

ground

are chassis

pads and via

3

33333

2

333

2

2222

2

22

22

HOLE TYPE 3

SFP_CAGE_20HOLE

HOLE TYPE 2

optional

plating

thru holes

ground

are chassis

pads and via

3

33333

2

333

2

2222

2

22

22

HOLE TYPE 3

SFP_CAGE_20HOLE

HOLE TYPE 2

ININ

ININ

ININ

P3V3

P3V3

IN

IN

BI

OUT

ININ

P3V3

P3V3

IN

OUT

IN

BI

AGND AGND

+

AGND AGND

+

1367073_1TYCO

VCCR

TD-TD+TX_DISVCCT

RATEMOD_DEF0MOD_DEF1MOD_DEF2

LOS

FAULTTX_

RD+RD-

SFP CONNECTOR

P3V3 P3V3 P3V3

AGND AGND

+

AGND AGND

+

P3V3 P3V3 P3V3 P3V3

1367073_1TYCO

VCCR

TD-TD+TX_DISVCCT

RATEMOD_DEF0MOD_DEF1MOD_DEF2

LOS

FAULTTX_

RD+RD-

SFP CONNECTOR

P3V3

OUTOUT

OUT

OUT

OUTOUT

OUT

OUT

P3V3 P3V3 P3V3 P3V3 P3V3 P3V3 P3V3 P3V3

P3V3P3V3

OUT

OUT

OUTOUT

P3V3P3V3P3V3P3V3P3V3

1367073_1TYCO

VCCR

TD-TD+TX_DISVCCT

RATEMOD_DEF0MOD_DEF1MOD_DEF2

LOS

FAULTTX_

RD+RD-

SFP CONNECTOR

AGND

+

AGND

P3V3

AGND

DPROM 1

GTS NODE CARD

R. ISOCRATE

08/13FPGA GFG / TRANSLATORS

DPROM 0

DIR=H --> A<==BDIR=L --> A==>B

21

ST2

21

ST1

81 RZ8 72 RZ8 63 RZ8

81 RZ7

72 RZ7

63 RZ7

54 RZ7

81 RZ6 72 RZ6 63 RZ6 54 RZ6

81 RZ4 72 RZ4 63 RZ4 54 RZ4

81 RZ5 72 RZ5 63 RZ5 54 RZ5

81 RZ3 72 RZ3 63 RZ3 54 RZ3

81 RZ2 72 RZ2 63 RZ2 54 RZ2

81 RZ1 72 RZ1 63 RZ1 54 RZ1

54 RZ8

21

C203

21

C1821

C1721

C1221

C11

21

R64

21

R63

21

R137

21

R139

1413121110987654321

J1

21

C204 21

C205 21

C206

1920

5174

6

18

8

11

13713

10

IC31

21

C14521

C14421

C143

1920

5174

6

18

8

11

13713

10

IC9

2524

2322201917161413

2627293032333536

481

1211986532

3738404143444647

IC1

2524

2322201917161413

2627293032333536

481

1211986532

3738404143444647

IC2

NC

GND=DGND

BTC_MD1_0BTC_RSEL_0

GND=DGND

VCC=P2V5

BTC_TXDIS_1BTC_MD1_1

100NF

CR_CON2_108_TDI FPGA_TDI

I23716V100NF

I236

CR_CON2_110_TDO

16V 16V

CR_CON2_111_FPGA_PROGRAM

100NF

MOLEX_87331

BTC_RSEL_2

100NF

BTC_RSEL_1

100NF

NC

TC_TXDIS_222

TC_RSEL_222

TC_TXDIS_322

TC_RSEL_322

TC_MD1_2NC

TC_MD1_3

BTC_LOS_0BTC_MD0_0BTC_TXF_0

TC_LOS_1TC_MD0_1TC_TXF_1

TC_LOS_0TC_MD0_0TC_TXF_0

TC_TXF_3TC_LOS_3

VCC=P2V5

TC_MD0_3

NCNC

TC_LOS_2TC_TXF_2

NCNC

NCNC

NCNC

BTC_TXF_3BTC_LOS_3

22

22

BTC_MD0_2 22NC

BTC_TXF_2BTC_LOS_2 22

22

BTC_TXDIS_2

BTC_TXDIS_3BTC_MD1_3

NC

BTC_RSEL_3

NC

22NCNC

BTC_TXDIS_0

NC

NCNC

TC_TXDIS_0TC_RSEL_0

22

22TC_MD1_0

TC_RSEL_1TC_TXDIS_1

22

22

NC

NC

100NF

4.7K

CR_CON2_104_TCKCR_CON2_112_FPGA_INIT

16V100NF 100NF

16V

CONCEPTHDL15.1X 0.00X

4.7K

100NF16V

16V

100NF

16V

4.7K

BTC_MD1_2

100NF

FPGA_CCLKFPGA_DONE

FPGA_DIN

16V

4.7K

NCNC

16V

CR_CON2_106_TMS

TC_MD1_1 22

22

22

22NC

22

NCNC 22

22222222 NCNC

22

BTC_MD0_3 22

22 NCNC

22

22

22

22NC

16V

BTC_LOS_1BTC_MD0_1BTC_TXF_1

22

NC

NCNC

TC_MD0_2

NC

PAGE:

DATE:

ABBREV:

TITLE:

1211 GENEVA 23

REF:

ETUDE:

5

D

B

1

D

8

8 7

7 6

6 5

4

4 3

3 2

2

1

CC

B

AA

EE

PCB: SYSTEM:REF:EDMS

IT/C

E

SWITZERLAND

DIV.

DESSIN:

VERSION:

131197531

42

6

108

1214

DGND DGND DGND DGND

P3V3

XCF04S

OE/RESET

CLK

P3V3

TDITMSTCK

VCCJVCCO

TDO

CEO*

DOCF*

GND

CE*

P2V5

DGNDDGNDDGND

P2V5

P3V3

DGND

XCF04S

OE/RESET

CLK

P3V3

TDITMSTCK

VCCJVCCO

TDO

CEO*

DOCF*

GND

CE*

DGNDDGND

INININ

INININ

74ALVC164245

2B<7>

2B<6>

2B<5>

2B<3>

2B<4>

2B<2>

2B<1>

2B<0>

2OE

1B<6>

1B<7>

1B<3>

1B<4>

1B<5>

1B<0>

1B<1>

1B<2>

1OE

2A<7>

2A<6>

2A<5>

2A<4>

2A<3>

2A<2>

2A<1>

2A<0>

2DIR

1A<7>

1A<6>

1A<3>

1A<4>

1A<5>

1A<0>

1A<1>

1A<2>

1DIR

INININ

IN

74ALVC164245

2B<7>

2B<6>

2B<5>

2B<3>

2B<4>

2B<2>

2B<1>

2B<0>

2OE

1B<6>

1B<7>

1B<3>

1B<4>

1B<5>

1B<0>

1B<1>

1B<2>

1OE

2A<7>

2A<6>

2A<5>

2A<4>

2A<3>

2A<2>

2A<1>

2A<0>

2DIR

1A<7>

1A<6>

1A<3>

1A<4>

1A<5>

1A<0>

1A<1>

1A<2>

1DIR

ININ

IN

P3V3

DGND

P3V3

DGND

PAD2PAD2

P2V5P2V5

ININ

IN

IN

OUTOUT

IN

OUT

OUTOUTOUT

OUTOUTOUT

OUTOUTOUT

OUTOUTOUT

OUT

IN

OUTOUT

OUTOUTOUT

OUTOUTOUT

ININ

P2V5P2V5 P2V5

P2V5

P3V3

DGND

P3V3

DGND

P2V5

DGND

P3V3

DGND

IN

P2V5P3V3

DGNDDGND

OUT

OUT

IN

ININ

INININ

IN

IN

OUT

09/13

R. ISOCRATE

SDRAM / FLASH MEMORIESGTS NODE CARD

21

54 RZ22

63 RZ22

81 RZ22

72 RZ22

21

C45

16

18

1539

535150484745444213111087542

19

3837

17

2120

36352234333231302926252423

IC30

16

18

1539

535150484745444213111087542

19

3837

17

2120

36352234333231302926252423

IC8

21

C194 21

C195 21

C196 21

C197 21

C198 21

C138 21

C14021

C141 21

C14221

C137 21

C13921

C135 21

C136

1 8

7523

IC26

21

C1932

1

C4421

C132

21

C199

55

15

43

53

1654

3634514946444038

525047454139

3533

14

292

31

19202223242526

5630

134

27

5678

101112131718

2832

IC7

3

48

1 2

7

56

IC28

SDRAM_DQML_0SDRAM_DQMH_1SDRAM_DQML_1

SDRAM_DQMH_0SDRAM_DQ15

100NF

SDRAM_DQ11SDRAM_DQ10

100NF16V 16V 16V

SDRAM_A4

16V100NF

GND=DGNDGND=DGND

SDRAM_DQ13SDRAM_DQ14

SDRAM_CS

SDRAM_A11

SDRAM_WE

SDRAM_DQ9SDRAM_DQ8SDRAM_DQ7SDRAM_DQ6SDRAM_DQ5SDRAM_DQ4

SDRAM_DQ0SDRAM_DQ1SDRAM_DQ2SDRAM_DQ3

SDRAM_DQ12

SDRAM_BA0

SDRAM_CLK

GND=DGND

SDRAM_A3SDRAM_A2

SDRAM_DQ16

SDRAM_A11

SDRAM_RAS

NC

VDDQ

=P3V

3VS

SQ=D

GND

SDRAM_WE

SDRAM_1_CLK22

SDRAM_0_CLK22

NC22

22 SDRAM_CLKX

SDRAM_A6SDRAM_DQ25SDRAM_DQ26SDRAM_DQ27SDRAM_DQ28SDRAM_DQ29

100NF

VSSQ

=DG

ND

SDRAM_RASSDRAM_A12

BOOT_STS

10K5%

EEPROM_SELEEPROM_WRITE

16V 16V100NF 100NF

BOOT_DQ15

BOOT_DQ0BOOT_DQ1

VDDQ

=P3V

3

SDRAM_DQ31

SDRAM_1_CLK

SDRAM_A8

SDRAM_A1

SDRAM_A9SDRAM_A7SDRAM_A5

SDRAM_A0SDRAM_BA1

SDRAM_A12

EEPROM_CLK

100NF

100NF

SDRAM_A10

SDRAM_A7

SDRAM_0_CLKSDRAM_CKE

BOOT_A24BOOT_BYTE

BOOT_DQ14BOOT_DQ13BOOT_DQ12BOOT_DQ11BOOT_DQ10BOOT_DQ9BOOT_DQ8BOOT_DQ6BOOT_DQ7BOOT_DQ5BOOT_DQ4BOOT_DQ3BOOT_DQ2

BOOT_A14

BOOT_WE

BOOT_A0

BOOT_A13BOOT_A15BOOT_A16BOOT_A17BOOT_A18BOOT_A19

BOOT_A23

SDRAM_DQ23

SDRAM_DQ20SDRAM_DQ18

SDRAM_DQ22

SDRAM_DQ19

100NF

SDRAM_A0SDRAM_BA1

100NF100NF16V16V

100NF16V100NF100NF

16V100NF16V

16V

EEPROM_DATA

EEPROM_HOLD

BOOT_CE2BOOT_RPBOOT_CE1BOOT_CE0

BOOT_A1BOOT_A3BOOT_A4

BOOT_A7BOOT_A8BOOT_A6BOOT_A5

BOOT_A9BOOT_A10BOOT_A11BOOT_A12

BOOT_A20BOOT_A22BOOT_A21

16V

16V16V

SDRAM_A4SDRAM_A5

SDRAM_A1

SDRAM_A6

SDRAM_A9

SDRAM_A3SDRAM_A2

SDRAM_CKE

SDRAM_CSSDRAM_CAS

SDRAM_A10

SDRAM_DQ17

SDRAM_DQ21

SDRAM_DQ24

BOOT_A2

BOOT_OE

100NF16V

CONCEPTHDL15.10.00 X

SDRAM_DQ30

EEPROM_Q

X

16V100NF

16V100NF

SDRAM_CAS

SDRAM_A8

SDRAM_BA0

PAGE:

DATE:

ABBREV:

TITLE:

1211 GENEVA 23

REF:

ETUDE:

5

D

B

1

D

8

8 7

7 6

6 5

4

4 3

3 2

2

1

CC

B

AA

EE

PCB: SYSTEM:REF:EDMS

IT/C

E

SWITZERLAND

DIV.

DESSIN:

VERSION:

DGND

P3V3

DGND

P3V3

DGND

P3V3

OUT

IN

INCY2305

REF

CLK3CLK4

CLK2

CLKOUTCLK1

P3V3

DGND

P3V3

DGND

P3V3

OUT

BIBIBIBIBIBI

BIBI

BI

OUT

BIBIBIBIBIBI

DGND

IN

IN

ININ

ININ

IN

ININ

IN

DGND

IN

IN

ININ

ININ

IN

ININ

INP3V3IN

IN

ININ

ININ

IN

ININ

IN

P3V3

ININ

DGND

P3V3P3V3

P3V3

DGND

P3V3

DGND

P3V3

BIBI

BI

BIBI

BIBI

BIBIBI

BIBI

BIBIBI

MT28F640J3

VSS<2-0>

STS

DQ14DQ15

DQ13DQ12DQ11DQ10

DQ9DQ8

DQ6DQ7

DQ5DQ4DQ3DQ2DQ1DQ0

A21

VCCQ

CEO

CE2

OE*

A1

VCC<1-0>

VPEN

RP*

A12

A14

WE*

CE1

A0

A2A3A4A5A6A7A8A9A10A11

A13

A15A16A17A18A19A20

A22A23A24BYTE*

BI

DQMLDQMH

DQ<14>DQ<13>DQ<12>DQ<11>DQ<10>

DQ<9>DQ<8>

DQ<15>

DQ<6>DQ<7>

DQ<5>

DQ<2>DQ<3>DQ<4>

DQ<1>DQ<0>

CKE

CASRAS

CLK

CSWE

A<10>

A<1>A<0>

A<5>

A<9>

A<4>A<3>A<2>

A<8>A<7>A<6>

BA0BA1

MT48LC16M16A2

A<11>A<12>

ININ

IN

ININININ

INININININININININININ

BI

ININININ

BIBIBIBI

IN

BIBIBIBIBIBIBIBIBIBI

IN

BIBI

DQMLDQMH

DQ<14>DQ<13>DQ<12>DQ<11>DQ<10>

DQ<9>DQ<8>

DQ<15>

DQ<6>DQ<7>

DQ<5>

DQ<2>DQ<3>DQ<4>

DQ<1>DQ<0>

CKE

CASRAS

CLK

CSWE

A<10>

A<1>A<0>

A<5>

A<9>

A<4>A<3>A<2>

A<8>A<7>A<6>

BA0BA1

MT48LC16M16A2

A<11>A<12>

DGND

P3V3

DGND

P3V3

IN

P3V3

DGND DGND

P3V3

DGND

P3V3

DGND

IN

P3V3

DGND

P3V3

DGND

P3V3

DGND

P3V3

DGND

P3V3

M95020

VCC

Q

HOLD*W*S*DC

VSS

GTS NODE CARDCARRIER CONNECTORS

R. ISOCRATE

10/13

CON1

3

2

1

L30

3

2

1

L32

3

2

1

L29

3

2

1

L31

114113112111110109108107106105104103102101100999897969594939291908988878685848382818079787776757473727170696867666564636261605958575655545352515049484746454443424140393837363534333231302928272625242322212019181716151413121110987654321

J8

114113112111110109108107106105104103102101100999897969594939291908988878685848382818079787776757473727170696867666564636261605958575655545352515049484746454443424140393837363534333231302928272625242322212019181716151413121110987654321

J7

VDD=VCN1B;VDD1=VCN1A VDD=VCN2B;VDD1=VCN2A

CR_CON2_112_FPGA_INITCR_CON2_109CR_CON2_107CR_CON2_105CR_CON2_103CR_CON2_100

CR_CON2_111_FPGA_PROGRAM

CR_CON2_095CR_CON2_093

CR_CON1_048

CR_CON1_087CR_CON1_083CR_CON1_081

NCNCCR_CON1_095CR_CON1_093

CR_CON1_077

VDD

:115

..119

;GN

D:1

20..1

24;V

DD

1:12

5..1

29

CR_CON1_090CR_CON1_094

CR_CON1_108CR_CON1_110CR_CON1_106

CR_CON2_030_SCLK_NCR_CON2_028_SCLK_P

MIC

TOR1

14PV

CR_CON2_018CR_CON2_016

CR_CON1_006 CR_CON2_005

CR_CON2_034

GND=DGND

CR_CON2_069

CR_CON1_016

CR_CON2_035

CR_CON2_029

CR_CON2_021

CR_CON2_052

CR_CON1_076

CR_CON1_058

CR_CON1_052

CR_CON2_010

CR_CON2_022CR_CON2_024

CR_CON2_040

CR_CON2_071CR_CON2_075

CR_CON2_081

CR_CON2_087

CR_CON2_096

CR_CON2_003

CR_CON2_009

CR_CON2_045

CR_CON2_104_TCKCR_CON2_106_TMSCR_CON2_108_TDICR_CON2_110_TDO

VDD

:115

..119

;GN

D:1

20..1

24;V

DD

1:12

5..1

29

GND=DGND

CR_CON2_089

CR_CON2_083

CR_CON2_077

CR_CON2_063CR_CON2_065

CR_CON2_059CR_CON2_057CR_CON2_053CR_CON2_051CR_CON2_047

CR_CON2_041CR_CON2_039

CR_CON2_033

CR_CON2_027CR_CON2_023

CR_CON2_017CR_CON2_015CR_CON2_011

CR_CON2_094CR_CON2_090CR_CON2_088CR_CON2_084CR_CON2_082CR_CON2_078CR_CON2_076CR_CON2_072CR_CON2_070

CR_CON2_064CR_CON2_066

CR_CON2_060CR_CON2_058CR_CON2_054

CR_CON2_048CR_CON2_046CR_CON2_042

CR_CON2_036

CR_CON2_012

CR_CON2_006CR_CON2_004

CR_CON1_070

CR_CON1_012

CR_CON1_004

100PF NFM60RI190

100PF NFM60RI189

100PF NFM60RI188

100PF NFM60RI187

CR_CON1_111CR_CON1_109

VCN2A

VCN2B

CR_CON1_112

CR_CON1_104

CR_CON1_054

CR_CON1_030

CR_CON1_078

CR_CON1_042

CR_CON1_036

CR_CON1_022

CR_CON1_051CR_CON1_053

CR_CON1_064

CR_CON1_107CR_CON1_103

CR_CON1_084

VCN1B

CR_CON1_015CR_CON1_011

VCN1A

CR_CON1_089

CR_CON1_069

CR_CON1_017

MIC

TOR1

14PV

CR_CON1_005CR_CON1_009 CR_CON1_010

CR_CON1_040

CR_CON1_046

CR_CON1_035

CR_CON1_029

CR_CON1_065

CR_CON1_060

CR_CON1_075CR_CON1_072

CR_CON1_027

CR_CON1_066

CR_CON1_033

CR_CON1_023CR_CON1_021

CR_CON1_018

CR_CON1_028

CR_CON1_034

CR_CON1_082

CR_CON1_088

CR_CON1_039CR_CON1_041CR_CON1_045CR_CON1_047

CR_CON1_024

CR_CON1_003

X CONCEPTHDL15.10.00X

CR_CON1_096

CR_CON1_105

CR_CON1_071

CR_CON1_059CR_CON1_063

CR_CON1_057

PAGE:

DATE:

ABBREV:

TITLE:

1211 GENEVA 23

REF:

ETUDE:

5

D

B

1

D

8

8 7

7 6

6 5

4

4 3

3 2

2

1

CC

B

AA

EE

PCB: SYSTEM:REF:EDMS

IT/C

E

SWITZERLAND

DIV.

DESSIN:

VERSION:

BIBI

BIBI

BIBI

BI

BI

BI

BIBI

BIBI

BIBI

OUT

BIBI

BI

BI

BIBI

BIBI

BIBI

BIBI

BI

BIBI

BIBI

BIBI

BIBI

BIBI

BI

BIBI

BIBI

BIBI

BIBI

BIBI

BIBI

BIBI

BI

BIBIBIBIBI

BI

BI

OUT

BIBI

BIBI

BIBI

BI

DGND

BI

BIBI

BIBI

BIBI

BIBI

BI

DGND

FILTER

BI

FILTER

FILTER

FILTER

VCC_BAR

VCC_BARVCC_BAR

VCC_BAR

DGND

BI

DGND

P3V3

P3V3

P3V3

P3V3

DGND

DGND

BI

IN

BIBI

DGND

2

864

1012

20181614

222426283032343638404244464850525456586062646668707274767880828486889092949698

100102104

112110108106

114

1

753

911

19

1517

13

2123

292725

31

39373533

4143

494745

5153

595755

6163

696765

7173

797775

8183

898785

9193

999795

101103

111

105107109

113

BI

BI

BIBI

BIBI

BIBI

BIBI

BI

BI

BI

BIBI

BIBI

BIBI

BIBI

BI

BI

BI

BIBI

BIBI

BIBI

DGND

BIBI

BI

BIBI

BI

BI

BI

BI

BI

BI

BIBI

BI

BIBI

BIBI

BIBI

BIBI

BIBI

BI

BIBI

BIBI

BIBI

IN

BIBI

BI

2

864

1012

20181614

222426283032343638404244464850525456586062646668707274767880828486889092949698

100102104

112110108106

114

1

753

911

19

1517

13

2123

292725

31

39373533

4143

494745

5153

595755

6163

696765

7173

797775

8183

898785

9193

999795

101103

111

105107109

113

GTS NODE CARD

GND_ENET

11/13

LED

ON

LED

10/1

00

ETHERNET 10/100 PHY

R. ISOCRATE

LED

ACT

RJ45 ETHERNET CONNECTORTHIS NET SHOULD BE A PLANE UNDER

21

QZ1

12

LD3

12

LD2

12

LD1

87654321

J2

21

R2921

R28 6 3RZ19

5 4RZ19

8 1RZ21

7 2RZ21

6 3RZ21

5 4RZ21

8 1RZ207 2RZ20

8 1RZ19

7 2RZ19

6 3RZ20

5 4RZ20

63

RZ18

81

RZ18

54

RZ18

72

RZ18

63

RZ17

81

RZ17

54

RZ17

72

RZ17

21

L33

21

L36

21

L35

21

L34

21

L1

21

C28

21

C29

21

C168

21

C169

21

C191

21

C192

21

C31 21

C32 21

C161 21

C162

C134

C63 21

R7

21

R9

21

R8

2

51

65

60595857

5456

55

31

1920

2324

29

28

27

30

32

26 45464748

53

49

52

4

1

17

3933

42

64

3

43

363738

6362

1615141312

IC6

21

R3

21

C621

C5

21

C4

21

R6

21

R5

21

C121

C3

21

R1

21

R42

1

C2

21

R2

16

11

15

10

14

9

3

8

2

7

1

6

IC13

PHY_CRSPHY_TX_CLK

PHY_TX_ERRPHY_COL22

2222

PHY_RX_ERR

22

VCCIO_ENET

51R

22

NCNC

PHY_TXD2

PHY_RX_DV22

PHY_RX_CLK2222

NCNC 22

22

PHY_RXD022

PHY_RXD122

PHY_RXD322

2222

22

500V1NF

51R

TFPIN

I201

1NF

22K

00

5%

PHY_SLW1TFPOP

PHY_TX_EN

PHY_TXD3PHY_TXD1PHY_TXD0

PHY_RESETPHY_SLW0

VCCTX_ENET

TFPONNC

NCNC

VCCA_ENET

51R 51R

500V

51R

270PF

50V

0.00

VCCIO_ENET

VCCA_ENET ILBB_0603

10UF

ILBB_06031000Z

ILBB_06031000Z 1000Z

ILBB_06031000Z

ILBB_06031000Z

VCCTX_ENETVCCD_ENET

50V10NF10NF

50V50V10NF

50V10NF10UF

16V100NF10UF

100NF16V

10UF

X X

22

22

CONCEPTHDL15.1

PHY_RXD2

PHY_MDC

22 22

TFPON

220R

PHY_MDO

I205

KPA-

2106

I206

KPA-

2106

270PF

TFPIN

TFPIP50V

500V

TFPOP

VCCD_ENET

220R220R

VCCD_ENET

KPA-

2106

RJ45_GND

1NF1NF

51RI203JACKAMP8FC

FE_3

2.21

532

.215

MHZ

18PF

18PF

PHY_MDINT

1/16W

TFPIP

1/16W5%

500V

GND=DGND

I208

PAGE:

DATE:

ABBREV:

TITLE:

1211 GENEVA 23

REF:

ETUDE:

5

D

B

1

D

8

8 7

7 6

6 5

4

4 3

3 2

2

1

CC

B

AA

EE

PCB: SYSTEM:REF:EDMS

IT/C

E

SWITZERLAND

DIV.

DESSIN:

VERSION:

VCC_BAR VCC_BAR

$PIN0

VCC_BAR

DGND

DGND DGND

OUTOUTOUTOUT

OUTOUTOUT

OUTOUTOUTOUT

BI

IN

INININININ

IN

IN

ININ

$PIN0

.

.

.

.

. .

. .

TG110S050N2

LXT971A

VCCA<1-0>

GND<8-0>

VCCIO<1-0> VCCD

TPFON

LED/CFG3

REFCLK/XI

ADDR3ADDR4

XO

MDDISRESET*TXSLEW0TXSLEW1ADDR0ADDR1ADDR2

RBIAS

TPFOP

TPFIPTPFINSD/TP*TDI

TDO

TMSTCKTRST*SLEEPPAUSE

LED/CFG2LED/CFG1

PWRDWN

MDIO

MDC

RXD3RXD2RXD1RXD0

RX_CLKRX_ER

TX_ER

TX_CLK

TX_ENTXD0TXD1TXD2TXD3

COLCRS

MDINT*

RX_DV

$PIN0

87654321

$PIN0

$PIN0

DGND

$PIN0

DGND

VCC_BAR

VCC_BAR

VCC_BAR VCC_BARVCC_BAR

DGND DGND

+

P3V3

DGND

+

DGND

P3V3

$PIN0

VCC_BAR

+

$PIN0

DGND

+

DGND

$PIN0 $PIN0

$PIN0

$PIN0

THIS NET SHORTEST AS POSSIBLE

PLACE THIS 100R RESISTOR

THESE TWO DECOUPLING CAPS SHOULDBE PLACED CLOSE TOGHETHER (EVERYWERE)

PECL HIGH (2,2V)

FPGA INPUT PINS

PLACE THIS 100OHM RESISTORAS NEAR AS POSSIBLE TO THESY98295 INPUT PINS (4,5)

PECL HIGH (2,2V)

R. ISOCRATE

GTS NODE CARDCLOCKS MANAGEMENT 12/13

SY1003P11 INPUT PINS (6,7)AS NEAR AS POSSIBLE TO THE

FPGA INPUT PINS

PLACE THIS 100OHM RESISTORAS NEAR AS POSSIBLE TO THE

FX200 INPUT PINS (1,2)

SY98295 INPUT PINS (4,5)AS NEAR AS POSSIBLE TO THEPLACE THESE 4 RESISTORS

PLACE THIS 100OHM RESISTORAS NEAR AS POSSIBLE TO THE

PLACE THIS 100OHM RESISTORAS NEAR AS POSSIBLE TO THE

THIS NET SHORTEST AS POSSIBLE

21

R86

21

R76

21

R85

21

R65

21

R82

21

R66

21

R140

21

R142

21

R141

21

R78

21

R77

21

R79

21

C156 21

C155

21

R33

21

R70

21

R69

21

R72

21

R71

21

R87

21

R88

21

R89

21

R90

21

R67

21

C150

21

R68

21

R74

21

R50

21

R49

1

TP23

21

C157

21

R84

21

R83

21

L10

21

L28

21

R48

21

R32

21

R31

21

C151

7

8

6

1112

2021

10

54

16

21

323130292726

3

2523

1415

IC10

7

8

6

1112

2021

10

54

16

21

323130292726

3

2523

1415

IC12

21

C158 21

C159 21

C160

21

R73

21

R75

21

C15321

C152

21

C40

21

C41 21

C42 21

C43

4 5 6

3

2

QZ2

21

C149

21

C14621

C14821

C147

9

1412

8

1110

7

1

16

2

IC32

21

C154

58

4

3

2

1

6

7

IC11

21

R81

21

R80

ILBB_06031000Z

10UF 50V

50V

560PF

CR_CON2_030_SCLK_N

CR_CON2_028_SCLK_P

FPGA_CLK_CLEAN_N

FPGA_CLK_CLEAN_P100NF16V

120R

120R120R

100R

120R

16V

130R130R

82R82R

4.7K

100NF100NF

DLY_3DLY_2DLY_1DLY_0

DLY_4

DLY_7DLY_6

130R130R

82R

100NF16V

10K

82R

100R

16V100NF16V16V

100NF

100R

4.7K

100NF16V

10K

NCNCNC

NCNC

DLY_8

DLY_5

DLY_9DLY_10

CLKREF_N

NCNCNCNCNCNCNCNCNCNCNC

NC

NCNCNCNCDLY_1_OUT_NDLY_1_OUT_P

FPGA_CLK_REF_OE

CONCEPTHDL15.1XX 0.00100R

CLKREF_P

100R

120R

16V

1000Z

120R120R

FPGA_CLK_RAW_P

FPGA_CLK_RAW_N

DLY_2_OUT_NDLY_2_OUT_P

100NF

50V50V16V100NF10UF

120R

10NF

100R

560PF

50V

120R

100NF16V 16V

100NF

SMH_OUT_P

ILBB_0603

1.0NF10NF50V

SMH_DISSMH_ISEL

SMH_LOCKED

100R

1.5K

5%1/16W

1/16W5%1.5K

SMH_OSEL

120R

SMH_OUT_N

120R

120R

120R

120R

1.0NF

PAGE:

DATE:

ABBREV:

TITLE:

1211 GENEVA 23

REF:

ETUDE:

5

D

B

1

D

8

8 7

7 6

6 5

4

4 3

3 2

2

1

CC

B

AA

EE

PCB: SYSTEM:REF:EDMS

IT/C

E

SWITZERLAND

DIV.

DESSIN:

VERSION:

DGND

P2V5P2V5

DGND

OUT

P2V5

DGND

IN

DGND

+

DGND DGND DGND DGND

LV1145BGND

VCCVOD+

E/D

VOD-

OUTIN

ININ

IN

IN

DGND

DGNDDGNDDGNDDGND

+

P3V3

DGND

DGND

FX_200

VCC

Q*Q

MONITORLD

OUT SEL

IN SELDISABLE

INCLN

GND<1-0>

DGNDDGND

DGNDDGND

DGND

P3V3

DGND

DGND

DGND

DGND

DGND DGND

P3V3

DGNDDGND

TP

P3V3

DGNDDGND

DGND

P3V3

SY100EP11UVCC

VEE

VEE

D

VCC

D*

Q0VEE

Q0*

Q1*

Q1

OUT

OUT

OUT

OUT

OUT

DGND

DGNDDGND

DGND

P3V3

DGND

P3V3

DGNDDGND

P3V3 P3V3

IN

SY89295U

QQ*

CASCADE

VEFVBB

CASCADE*

EN*SETMAXSETMINLEN

IN*VCF

IND10D9

D7D8

D6D5D4D3D2D1D0

GND<2-0>

VCC<3-0>

IN

ININ

ININ

IN

ININININ

DGND

SY89295U

QQ*

CASCADE

VEFVBB

CASCADE*

EN*SETMAXSETMINLEN

IN*VCF

IND10D9

D7D8

D6D5D4D3D2D1D0

GND<2-0>

VCC<3-0>

DGND

P2V5

DGND

P2V5

DGND

P2V5 P2V5

DGNDDGND

DGND

P2V5

P3V3

13/13

R. ISOCRATE

POWER SUPPLYGTS NODE CARD

VTTTX_MGT=2,5V

VTTRX_MGT=1,7V

GND_MGT

21

R20

21

R24

21

R23

12

LD4

12

LD8

12

LD7

12

LD6

2

1

3 T1

2

1

3 T5

2

1

3 T4

2

1

3 T3

21

L27

21

C34

21

C33

21

C30

21

C37

21

C39

21

C38

21

C200

21

C133 21

C184 21

C36 21

C35 21

C176

21

C208

21

C207 21

C62 21

C131 21

C75 21

C64 21

C65

21

C9921

C9821

C201

21

C202

21

R10

21

R11

21

R18

21

R19

21

R16

21

R17

21

R14

21

R15

5 21

8

4

IC3

21

R21

1

42

3

5

IC29

5 21

8

4

IC5

1

42

3

5

IC34

1

42

3

5

IC33

10NF

6.3V1.0UF

220R

4.7UF

VTTTX_MGT

KPA-2106

KPA-2106

1.0K

6.3V1.0UF

6.3V6.3V330UF

2.5V

330UF

KPA-2106

KPA-2106

BSS138

BSS138

BSS138

BSS138

USER_LED0

0.00

4.7UF

50V10NF

50V

470

47UF

VTTRX_MGT

47UF

2.5V

6.3V 6.3V 6.3V1.0UF

1.0UF6.3V

USER_LED3

USER_LED1

330R

220R

330R

220R

330R

330R

220R

1.5V

X X CONCEPTHDL15.1

USER_LED2

ILBB_06031000Z

1.0UF6.3V

6.3V

1.0UF6.3V

1.0UF 1.0UF 1.0UF 1.0UF6.3V

1.0UF330UF6.3V 6.3V

1.0UF 1.0UF 1.0UF

1.0K

1.0K

PAGE:

DATE:

ABBREV:

TITLE:

1211 GENEVA 23

REF:

ETUDE:

5

D

B

1

D

8

8 7

7 6

6 5

4

4 3

3 2

2

1

CC

B

AA

EE

PCB: SYSTEM:REF:EDMS

IT/C

E

SWITZERLAND

DIV.

DESSIN:

VERSION:

DGNDDGNDDGND

+

IN

LT1763GND<2-0>

OUTSENSE/ADJ

BYPSHDN*IN*

DGND

P2V5 P3V3

IN

DGND

IN

SENSE

OUT

LT1764A

GND

SHDN ADJ

P2V5 P3V3

IN

DGND

IN

SENSE

OUT

LT1764A

GND

SHDN ADJ

P2V5 P3V3

IN

P2V5 P3V3

DGND

P1V5

VCC_BAR

VCC_BAR

AGNDDGND

P2V5A

P3V3LT1763GND<2-0>

OUTSENSE/ADJ

BYPSHDN*IN*

DGND DGND

P2V5

DGND

DGNDDGND

P3V3

P3V3

DGND

P3V3

IN

SENSE

OUT

LT1764A

GND

SHDN ADJ

DGND

P3V3

DGND

+

DGND

+

DGND

+

+

DGND

+

DGND DGND DGND DGND DGND

DGND

DGND

+

DGND DGND DGND DGND DGND DGND

DGND

21

R44

21

R42

21

R43

21

R35

21

R41

21

R40

21

R36

21

R37

21

R39

21

R38

21

R34

21

R30

23

8

67

4

1

5

IC24

23

8

67

4

1

5

IC21

23

8

67

4

1

5

IC18

23

8

67

4

1

5

IC15

21

R105

21

R104

21

C187

21

R101

21

R100

21

C180

21

R97

21

R96

21

C171

21

C16421

R92

21R93

5

16

6

15

109

1112

3

42

1

IC25

21

C189 21

C190

21

R106

21

C185

5

16

6

15

109

1112

3

42

1

IC22

21

C182 21

C1832

1R1

02

21

C178

21

R103

21

C188

5

16

6

15

109

1112

3

42

1

IC23

21

C186

21

R99

21

C181

5

16

6

15

109

1112

3

42

1

IC20

21

C179

5

16

6

15

109

1112

3

42

1

IC192

1C173 2

1

C174

21

R98

21

C170

21

R95

21

C172

5

16

6

15

109

1112

3

42

1

IC17

21

C175

21

C27

21

R94

21

C163 21

C16521

C16721

C166

21

R91

5

16

6

15

109

1112

3

42

1

IC14

5

16

6

15

109

1112

3

42

1

IC16I224040210NF

50V16V

I881.1K

I67

5%1/16W 1/16W

100R

100R

100R

100R

TST_RXP_0

16V

0402

120R

120R

120R

120R

120R

120R

120R

120R

TST_RXN_3TST_RXP_3

I305

MGT_TXDP_1

TST_TXP_1TST_TXN_1TX_SEL1_1

MGT_TXDN_1

TX_SEL0_1

TX_SEL1_0

GND=AGND

16V

100NF 0402

MGT_RXDP_1MGT_RXDN_1

16V

TRC_TXP_2

PAD_TXP_2

GND=AGND

MGT_TXDP_2TX_SEL0_2

X XXX

GND=AGND

GND=AGND

GND=AGND

GND=AGND

GND=AGND

GND=AGND

SWOUTN_0

0402 I172

1MNC

I85I1

TX_SEL0_0

16V 16V0402100NF100NF100NF

0402

RX_SEL0_0TRC_RXP_0

PAD_RXP_0TRC_RXN_0

1.0K

5%

TRC_TXN_1

RX_SEL1_0

MGT_RXDN_0NC

PAD_TXP_1

0402100NF

1/16W

1/16W

I89

1%1M

1.1K

I227

NCTX_SEL1_3TST_TXN_3

NC

MGT_TXDP_3NC

MGT_TXDN_3

TX_SEL0_3

TRC_TXN_2

TX_SEL1_2TST_TXN_2

NC

NCMGT_TXDN_2

NC1M1%

1M

1/16W1%1M

1%

0402100NF

1M

100NF04020402I208

PAD_RXP_1

TST_TXP_2

TST_TXP_3

I110

5%1.0K

5%

1.1K1.0K1/16W5%

5%1.1K

I86

5%1/16W1.0K

I237

1M

1/16W5%

MGT_RXDP_2MGT_RXDN_2

PAD_RXN_1

1/16W

I117100NF0402I121

I164

040216V

16V0402100NFI102

I301

I303

I304

SWOUTP_1

SWOUTP_2SWOUTN_2

SWOUTN_1

I1240402

PAD_RXP_3

PAD_RXN_0 SWOUTP_ONC TST_RXN_0

TST_RXP_1TST_RXN_1

I143100NF

16V0402100NF

TST_RXN_2TST_RXP_2

16V0402100NFI95

TRC_TXP_0TRC_TXN_0

PAD_TXN_0PAD_TXP_0

TRC_TXP_1

I133I131

1%

TRC_RXP_1RX_SEL0_1

50V16V

10NF

1/16W RX_SEL1_1

MGT_RXDP_0

I186I194

16V0402 0402

RX_SEL1_2NC

PAD_RXN_2

TRC_RXN_1

1/16W

0402

PAD_RXP_2

GND=AGND100NF

I197

PAD_TXN_21/16W1%1M

10NF100NF100NF

TRC_RXN_2TRC_RXP_2RX_SEL0_2

50V16V 16V

0402I232I158I182

I151GND=AGND

GND=AGND

I212100NF

PAD_TXP_3

0402100NF0402I215

16V16V16V

TRC_TXP_3TRC_TXN_3

1%

TRC_RXN_3TRC_RXP_3RX_SEL0_3

50V10NF

I177100NFI204

PAD_TXN_31/16W 1/16W RX_SEL1_3

PAD_RXN_3SWOUTN_3

1/16W

SWOUTP_3

MGT_RXDN_3MGT_RXDP_3

1/16W1%

100NF16V16V

0402

GND=AGND

PAD_TXN_1NC

NC

TST_TXN_0TST_TXP_0

MGT_TXDP_0MGT_TXDN_0

16V0402100NF

PAGE:

DATE:

ABBREV:

TITLE:

1211 GENEVA 23

REF:

ETUDE:

5

D

B

1

D

8

8 7

7 6

6 5

4

4 3

3 2

2

1

CC

B

AA

EE

PCB: SYSTEM:REF:EDMS

IT/C

E

SWITZERLAND

DIV.

DESSIN:

VERSION:

OUTOUT

OUT

IN

OUTOUT

INSY58023U

Q1*

VCC<1-0>

GND<1-0>

Q1VT1IN1*SEL1

IN1IN0*

IN0VT0

SEL0Q0

Q0*IN

IN

IN

IN

AGND

AGND AGND

AGND AGND

AGND AGND

AGNDAGND

P2V5A

P2V5A

P2V5A

SY58601U

GND

VCC

VT

IN

IN*

VREF_ACQ

Q*

SY58601U

GND

VCC

VT

IN

IN*

VREF_ACQ

Q*

SY58601U

GND

VCC

VT

IN

IN*

VREF_ACQ

Q*

P2V5A

SY58601U

GND

VCC

VT

IN

IN*

VREF_ACQ

Q*

AGND AGND AGND AGND

AGNDAGNDAGNDAGND

AGND

AGND

AGNDAGNDAGNDAGND

AGND

AGND

AGND AGND AGND AGND

AGND

AGNDAGND

AGND

AGND

AGNDAGND

AGNDAGND

AGNDAGND

P2V5A

P2V5A

P2V5A

P2V5A

P2V5A

P2V5A

P2V5A

P2V5A

P2V5AP2V5AP2V5AP2V5A

P2V5A

P2V5AP2V5AP2V5AP2V5A

P2V5A

P2V5AP2V5AP2V5AP2V5A

P2V5A

P2V5A

P2V5A P2V5A P2V5A P2V5A

P2V5A

AGND

P2V5A

AGND

P2V5A

AGND

P2V5A

AGND

ININ

IN

ININ

IN

SY58023U

Q1*

VCC<1-0>

GND<1-0>

Q1VT1IN1*SEL1

IN1IN0*

IN0VT0

SEL0Q0

Q0* OUTOUT

ININ

IN

ININ

IN

SY58023U

Q1*

VCC<1-0>

GND<1-0>

Q1VT1IN1*SEL1

IN1IN0*

IN0VT0

SEL0Q0

Q0* OUTOUT

IN

ININ

IN

SY58023U

Q1*

VCC<1-0>

GND<1-0>

Q1VT1IN1*SEL1

IN1IN0*

IN0VT0

SEL0Q0

Q0* OUTOUT

OUTOUT

OUT

IN

IN

ININ

SY58023U

Q1*

VCC<1-0>

GND<1-0>

Q1VT1IN1*SEL1

IN1IN0*

IN0VT0

SEL0Q0

Q0*

IN

OUTOUT

OUTOUT

IN

ININ

IN

ININ

IN

SY58023U

Q1*

VCC<1-0>

GND<1-0>

Q1VT1IN1*SEL1

IN1IN0*

IN0VT0

SEL0Q0

Q0*

IN

OUTOUT

IN

IN

IN

ININ

SY58023U

Q1*

VCC<1-0>

GND<1-0>

Q1VT1IN1*SEL1

IN1IN0*

IN0VT0

SEL0Q0

Q0*OUTOUT

OUTOUT

SY58023U

Q1*

VCC<1-0>

GND<1-0>

Q1VT1IN1*SEL1

IN1IN0*

IN0VT0

SEL0Q0

Q0*

Related Documents