[Type text] Page 1 DEPARTMENT OF COLLEGIATE AND TECHNICAL EDUCATION DEPARTMENT OF ELECTRONICS & COMMUNICATIONS ENGINEERING STUDY MATERIAL ON DIGITAL ELECTRONICS (15EC32T) UNIT 1: COMBINATIONAL LOGIC CIRCUITS Prepared by SMT. SAVITA NAIK LECTURER, E&CE DEPT GOVERNMENT POLYTECHNIC, RAICHUR-117 DIST:-RAICHUR-584101 2020-2021

Welcome message from author

This document is posted to help you gain knowledge. Please leave a comment to let me know what you think about it! Share it to your friends and learn new things together.

Transcript

[Type text] Page 1

DEPARTMENT OF COLLEGIATE AND TECHNICAL

EDUCATION

DEPARTMENT OF ELECTRONICS & COMMUNICATIONS ENGINEERING

STUDY MATERIAL ON

DIGITAL ELECTRONICS

(15EC32T)

UNIT 1: COMBINATIONAL LOGIC CIRCUITS

Prepared by

SMT. SAVITA NAIK

LECTURER, E&CE DEPT

GOVERNMENT POLYTECHNIC, RAICHUR-117

DIST:-RAICHUR-584101

2020-2021

Digital Electronics (15EC32T)

DEPT ECE,GPT RAICHUR Page 2

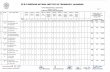

CONTENTS

S.NO CHAPTERS

Page no.

01 COMBINATIONAL LOGIC CIRCUITS

1.1 COMBINATIONAL CIRCUITS

3

1.2 MULTIPLEXERS

3-4

1.3. 2-Input Multiplexer (2:1 Multiplexer)

4

1.4. Realization Of Gates Using 2:1 Multiplexer

5-6

1.5 Realization Of Gates Using 4:1 Multiplexer

6-7

1.6 Realization Of Higher –Order Multiplexer Using Lower-Order Multiplexer Ics.

8-11

1.7. Multiplexer ICS And Features.

11

1.8. Applications Of Multiplexers

12

1.9 Demultiplexer

13

1.20 . Realization Of 1:2 Demultiplexer.

14

1.21. Demultiplexer Ics

14

1.22 Applications Of Demultiplexers

15

1.23. Encoder

15

1.24 Decimal-To- BCD Encoder

16

1.25: Decimal- To – BCD Priority Encoder (4-Input Priority Encoder)

17-19

1.26 . Encoder Ics And Their Features.

19

1.27. Applications Of Encoder

20

1.28. Decoder

20-21

1.29: BCD-TO SEVEN SEGMENT DECODER

21-24

1.30 : Decoder Ics And Their Features

25-26

Digital Electronics (15EC32T)

DEPT ECE,GPT RAICHUR Page 3

UNIT: 1

COMBINATIONAL LOGIC CIRCUITS

1.1 Combinational circuits

Combinational switching circuits are those whose output levels at any instant of time are

dependent only on the level present at the inputs at that time .Any prior input level

conditions have no effect on the present outputs, because combinational logic circuits have

no memory. Examples are logic gates, adders, subtractors, comparators, encoders, decoders,

multiplexers and demultiplexers. A combinational circuits can have a n number of inputs

and m number of outputs as shown in fig:1 .

Fig:1 Combinational logic circuit.

1.2 MULTIPLEXERS

The term Multiplex means “many into one”. Multiplexing is the process of transmitting a

large number of information over a single line . A digital multiplexer is a combinational

circuit that select one digital information several sources and transmits the selected

information on a single output line. A multiplexer is also called a data sector. The

multiplexer has several data input lines and single output line. The routing of the desired

data input to the output is controlled by SELECT (control) inputs. The relation between

number of select lines and number of data inputs are 2m

= n .

2 to 1

MUX

4 to 1

MUX

Fig: 1.1 . Logic Symbol for multiplexer.

1.3. 2-Input Multiplexer (2:1 Multiplexer)

Fig: 1.3: 2-Input

Multiplexer

Fig.1.3 shows the logic symbol, logic circuit and functional table for a 2-input

multiplexer. The circuit consists of two AND gates G1 and G2, an OR gate G3 and a NOT gate

G4. I0 and I1 are the data inputs and S is the data select input . The logic level applied to the S

input enable one of the two And gates and allows data input to pass through the OR gate to the

output Y . Boolean expression for output Y is

Y= E(S‟I0 +SI1) --------- (1)

When S=0, gate G4 outputs a 1 to gate G1 and a 0 to gate G2 . Thus G1 is enabled and

G2 is disabled. Data from input line I0 goes to output line Y and from I1 is blocked .

Substituting S=0 in equation (1),

Y= 1(1.I0 +0.I1)

= I0 ----- (2)

This shows that output Y follows input I0.

When S=1, gate G4 outputs a 0 to gate G1 and a 1 to gate G2 . Thus G1 is disabled and G2 is

enabled. Data from input line I1 goes to output line Y and from I0 is blocked . Substituting S=0

in equation (1), AND gate G1 is disabled and G2 is enabled. Substituting S=1 in equation (1)

Y= 1(0.I0 +1.I1)

= I1 ----- (3)

This shows that output Y follows input I1.

Digital Electronics (15EC32T)

DEPT ECE,GPT RAICHUR Page 5

1.4. Realization of Gates using 2:1 Multiplexer

(a) Implementation of NOT gate using 2 : 1 Mux

We can analyze it Y = x’.1 + x.0 = x’ It is NOT Gate using 2:1 MUX. The implementation of NOT gate is done using “n” selection lines.

(b) Implementation of AND gate using 2 : 1 Mux

c) Implementation of OR gate using 2 : 1 Mux using “n-1” selection lines.

d) Implementation of NAND gate using 2 : 1 Mux

Implementation of NAND, NOR, XOR and XNOR gates requires two 2:1 Mux. First

multiplexer will act as NOT gate which will provide complemented input to the second

multiplexer.

Digital Electronics (15EC32T)

DEPT ECE,GPT RAICHUR Page 6

e) Implementation of NOR gate using 2 : 1 Mux

f) Implementation of EX-OR gate using 2 : 1 Mux

Digital Electronics (15EC32T)

DEPT ECE,GPT RAICHUR Page 7

g) Implementation of EX-NOR gate using 2 : 1 Mux

1.5 Realization of Gates using 4:1 Multiplexer

Digital Electronics (15EC32T)

DEPT ECE,GPT RAICHUR Page 8

Fig: 1.4 Implementation of gates using 4:1 mux.

1.6 Realization of higher –order multiplexer using Lower-order multiplexer Ics.

Now, let us implement the following two higher-order Multiplexers using lower-order

Multiplexers.

8x1 Multiplexer

16x1 Multiplexer

8x1 Multiplexer

In this section, let us implement 8x1 Multiplexer using 4x1 Multiplexers and 2x1

Multiplexer. We know that 4x1 Multiplexer has 4 data inputs, 2 selection lines and one

output. Whereas, 8x1 Multiplexer has 8 data inputs, 3 selection lines and one output.

So, we require two 4x1 Multiplexers in first stage in order to get the 8 data inputs.

Since, each 4x1 Multiplexer produces one output, we require a 2x1 Multiplexer in

second stage by considering the outputs of first stage as inputs and to produce the final

output.

Let the 8x1 Multiplexer has eight data inputs I7 to I0, three selection lines s2, s1 & s0 and

one output Y. The Truth table of 8x1 Multiplexer is shown below.

Selection Inputs Output

S2 S1 S0 Y

0 0 0 I0

0 0 1 I1

0 1 0 I2

0 1 1 I3

1 0 0 I4

1 0 1 I5

1 1 0 I6

1 1 1 I7

We can implement 8x1 Multiplexer using lower order Multiplexers easily by considering

the above Truth table. The block diagram of 8x1 Multiplexer is shown in the following

figure.

Digital Electronics (15EC32T)

DEPT ECE,GPT RAICHUR Page 9

Fig: 1.5 implement 8x1 Multiplexer using 4x1 Multiplexers and 2x1 mux

The same selection lines, s1 & s0 are applied to both 4x1 Multiplexers. The data

inputs of upper 4x1 Multiplexer are I7 to I4 and the data inputs of lower 4x1 Multiplexer are I3 to

I0. Therefore, each 4x1 Multiplexer produces an output based on the values of selection lines, s1 &

s0. The outputs of first stage 4x1 Multiplexers are applied as inputs of 2x1 Multiplexer that is

present in second stage. The other selection line, s2 is applied to 2x1 Multiplexer.

If s2 is zero, then the output of 2x1 Multiplexer will be one of the 4 inputs I3 to I0 based

on the values of selection lines s1 & s0.

If s2 is one, then the output of 2x1 Multiplexer will be one of the 4 inputs I7 to I4 based

on the values of selection lines s1 & s0.

Therefore, the overall combination of two 4x1 Multiplexers and one 2x1 Multiplexer performs

as one 8x1 Multiplexer.

1.7 16x1 Multiplexer

In this section, let us implement 16x1 Multiplexer using 8x1 Multiplexers and 2x1

Multiplexer. We know that 8x1 Multiplexer has 8 data inputs, 3 selection lines and one output.

Whereas, 16x1 Multiplexer has 16 data inputs, 4 selection lines and one output. So, we require

two 8x1 Multiplexers in first stage in order to get the 16 data inputs. Since, each 8x1

Multiplexer produces one output, we require a 2x1 Multiplexer in second stage by considering

the outputs of first stage as inputs and to produce the final output. Let the 16x1 Multiplexer has

sixteen data inputs I15 to I0, four selection lines s3 to s0 and one output Y. The Truth table of

16x1 Multiplexer is shown below.

Digital Electronics (15EC32T)

DEPT ECE,GPT RAICHUR Page 10

Selection Inputs

Output

S3 S2 S1 S0 Y

0 0 0 0 I0

0 0 0 1 I1

0 0 1 0 I2

0 0 1 1 I3

0 1 0 0 I4

0 1 0 1 I5

0 1 1 0 I6

0 1 1 1 I7

1 0 0 0 I8

1 0 0 1 I9

1 0 1 0 I10

1 0 1 1 I11

1 1 0 0 I12

1 1 0 1 I13

1 1 1 0 I14

1 1 1 1 I15

We can implement 16x1 Multiplexer using lower order Multiplexers easily by

considering the above Truth table. The block diagram of 16x1 Multiplexer is shown in the

following figure.

Digital Electronics (15EC32T)

DEPT ECE,GPT RAICHUR Page 11

Fig: 1.6

implement 16x1 Multiplexer using 8x1 Multiplexers and 2x1.

1.7. Multiplexer ICS and features.

Multiplexers are available as MSI- IC format. The table indicates Multiplexer IC

numbers for TTL logic family.CMOS Multiplexer ICs are also popular amongst the Digital

Digital Electronics (15EC32T)

DEPT ECE,GPT RAICHUR Page 12

system designer because of low power consumption. Below table indicates list of few CMOS

multiplexer ICs.

1.8. Applications of multiplexers

Multiplexer or data selectors are combinational circuits which transfer data from many

sources to output under the control of data select lines. Multiplexer has many applications right

from data routing, time division multiplexing, function generator to parallel to serial converter

etc. A single multiplexer can replace several logic gates ICs, saving PCB area, interconnections,

design efforts and cost. A list of popular applications is given below.

1. Data routing

2. Data bussing

3. Switch setting comparator

4. Multiplexer as a function generator

5. Parallel to serial converter

6. Cable TV signal distribution

7. Telephone network

8. Sharing printer /resources

1.9 Demultiplexer

Demultiplexer has a single input and n output lines. Demultiplexer can be visualized as

reverse multi-position switch. The select lines permit input data from single line to be switched

to any one of the many output lines as shown in fig.

Digital Electronics (15EC32T)

DEPT ECE,GPT RAICHUR Page 13

Fig: 1.7 . Multi-position switch as Demultiplexer

Demultiplex means one into many. A demultiplexer reverses the multiplexing operation.

In other words, the demultiplexer takes one data input source and selectively distributes it to 1 of

N output channels just like multi-position switch. It also has „m’ select lines for selecting the

desired output for the input data as shown in fig. 1.8 .The mathematical relation between select

lines and „n’ output are: 2m

= n

Figure 1.8: Logic symbol of basic demultiplexer

As a demultiplexer takes data from one input line and distributes over a 2m output line,

hence it is often referred to as 1 to 2m line converter. There are four basic types

demultiplexers: 1 to 2 demultiplexer, 1 to 4 demultiplexer, 1 to 8 demultiplexer and 1 to 16

demultiplexer .

1.20 . Realization of 1:2 Demultiplexer.

Digital Electronics (15EC32T)

DEPT ECE,GPT RAICHUR Page 14

Fig:1.9 - 1:2 Demultipexer

Fig 1.9 (a),(b),(c) and (d) shows the logic symbol, function table ,logic diagram and

Boolean expression respectively,for 1:2 demultiplexer. The input data bit is labelled D . The

input data line is connected to both AND gates . The select line S enables only one gate at a

time. The data D will pass through the enabled gate to the output line. When S=0 the upper And

gate is enabled while the lower and gate is disabled. Therefore data bit D is transmitted only to

the Y0 output, giving Y0=D . If D is low ,Y0 is low . If D is high, Y0 is high . The value of Y0

depends on value of D . The other output Y1 is low state . If control input is changed to S=1, the

lower AND gate is enabled while the upper AND gate is disabled. Then D is transmitted only to

the Y1 output and Y1=D. The Boolean expressions for the output as follows:

Y0=S‟D

Y1=SD

1.21. Demultiplexer ICs

So far we have discussed construction of demultiplexers using discreet logic gates.

Commercially,demultiplexers are available as MSI- IC format. Below indicates a table of

demultiplexer IC numbers for TTL logic family.

CMOS ICs provide a combination of Multiplexer and Demultiplexer in a single chip IC.

These are also popular amongst the Digital system designer because of low power consumption.

Digital Electronics (15EC32T)

DEPT ECE,GPT RAICHUR Page 15

1.22 Applications of Demultiplexers

Digital demultiplexers are combinational devices controlled by a selector address that

routes input data to one of many outputs of the demultiplexers. These can be used in following

applications.

1. Data demultiplexing

2. Clock demultiplexing

3. Memory addressing

4. Four phase clock generator

5. Function generation using DMUX

6. Switch encoding

7. Serial to parallel converter

1.23. ENCODER

The process of converting from human readable code to machine readable code i.e.

binary is known as encoding. An encoder is a combinational circuit that coverts more familiar

numbers, symbols or character into binary code. An encoder has a number of input lines but only

one of them is activated at a time representing a digit or character and produces a binary code

depending on which input is activated. Figure 1.20 is the logic symbol of encoder with „m‟

inputs and „n‟ outputs. In short, it is multiple inputs and multiple outputs device with proper

conversion system. Note that encoder performs the reverse operation of the decoder. An encoder

has „m‟ number of input lines and „n‟ number of output lines. The numbers of outputs (n) are

always less than number of inputs (m). Some of the most commonly used encoders are – (1)

Linear encoders are octal to binary, Decimal to BCD and Hexadecimal to binary where normal

encoding is implemented and (2) Priority encoders.

Digital Electronics (15EC32T)

DEPT ECE,GPT RAICHUR Page 16

1.24 Decimal-To- BCD Encoder

A decimal to BCD (binary coded decimal) encoder is also known as 10-line to 4-line

encoder. It accepts 10- inputs and produces a 4-bit output corresponding to the activated decimal

input. Figure-1.21 shows the logic symbol of decimal to BCD encoder.

Fig: 1.21: logic symbol of decimal to BCD encoder

The truth table of Decimal to BCD encoder is shown in below Table . There are ten

inputs corresponding 10 decimal inputs (I0, I1, I2, I3, I4, I5, I6, I7, I8, I9) and 4 Outputs (Y0,

Y1, Y2,Y3). The encoder assumption that only one of the inputs is activated (logic 1) and other

inputs are not activated (i.e. at logic 0).

Table for Decimal to BCD Encoder

In the truth table, the input variable I0 represents the least significant digit (LSD) and and

I9 represents most significant digit (MSD). Similarly, in the outputs Y0 represents least

significant bit (LSB) and Y3 is the most significant bit (MSB). The truth table includes only all

valid combinations of the inputs. The valid combinations are those which have exactly one input

Digital Electronics (15EC32T)

DEPT ECE,GPT RAICHUR Page 17

equal to logic 1 while all other inputs are logic 0‟s.As the number of inputs is 10, K-maps cannot

be used to derive the Boolean expressions. The Boolean expression can be directly derived from

the truth table by visual inspection. Let us obtain the Boolean expression for each output.

Output Y0 is 1 if any of the inputs I1 or I3 or I5 or I7 is 1. Then, the Boolean expression

Y0 = I1 +I3 +I5 +I7 +I9

Similarly,

Y1 = I2 +I3 +I6 +I7 , Y2 = I4 +I5 +I6 +I7, Y3 = I8 +I9

From these Boolean expressions, the Decimal to BCD Encoder can be implemented by using

simply three 4 OR gates. Figure-1.22 indicates the logic diagram for Decimal to BCD Encoder.

Fig: 1.22: logic diagram for Decimal to BCD Encoder

1.25: Decimal- to – BCD priority encoder (4-Input Priority Encoder)

This Priority encoder consists of 4 inputs and three outputs. Although an encoder has

2n

inputs and n outputs, it has a third output „V‟ which is a valid bit indicator and is set to one

when one or more inputs are active or equal to 1. This valid bit is zero when all the inputs are

zero which indicates that there is no valid input. On this condition, other outputs are considered

as don‟t care conditions and are not inspected when V is zero. The highest will be the priority of

the input with a higher subscript number according to the truth table that is most significant bit

will have highest priority while the least significant bit will have low priority .

In the truth table, D3 has the highest priority and D0 has lowest priority. When D3 is

active or 1, then regardless of other inputs, the output is 11. The next higher priority is D2 after

D3. The next higher priority is D2 after that D1. Thus, when D3 is 0 and D2 is 1 then regardless

Digital Electronics (15EC32T)

DEPT ECE,GPT RAICHUR Page 18

of other two inputs (which has lower priority), the output is 10. When higher priority inputs are

zero then the output for D1 is generated and so on down the priority levels.

From the above truth table we can write the Boolean expression for the two outputs as

K-map Simplification

The above expressions for the inputs and valid output can be obtained by using the K-

map simplification. Although the truth table of this encoder is shown with five rows, we can

obtain 16 input combinations when each × in each row is replaced first with zero and then by

one. The min terms of the two outputs can be derived as

Y1 = ∑ m (1, 2, 3, 5, 6, 7, 9, 10, 11, 13, 14, 15) Y0 = ∑ m (1, 3, 4, 5, 7, 9, 11, 12, 13, 15)

Then from the below K-maps we obtain the outputs as

Y1 = D3 + D2

Digital Electronics (15EC32T)

DEPT ECE,GPT RAICHUR Page 19

The logic diagram of 4-input priority encoder is implemented by corresponding output

expressions obtained from K-map simplification. A circuit diagram of this encoder is shown

below.

Fig: 1.23: 4- bit priority encoder .

Digital Electronics (15EC32T)

DEPT ECE,GPT RAICHUR Page 20

1.26 . Encoder ICs and their features.

IC 74147 Decimal-to-BCD Priority Encoder

Ic 74147 fuctions as a decimal-to- BCD priority encoder. It has Nine active low inputs

representing the decimal digit 1 throgh 9. It produces inverted BCD code corresponding to the

highest numbered activated input . The IC 74147 outputs will normally be HIGH when none of

the input is activated . This corresponds to the decimal 0 input condition . There is no input since

the encoder assume decimal 0 input state when all inputs are HIGH . The 74147 outputs can be

converted to normal BCD by inverting them .

1.27. Applications of Encoder

Encoders are normally preferred where there is a need to convert information of code

from one format to another. In addition to linear and priority encoders, encoders have many

applications as listed below.

1. Keyboard encoder for computers

2. Optical encoders –linear or rotary

3. Interfacing peripherals to microprocessors

4. Audio/video coding and transmission

1.28. Decoder

Decoder is a combinational logic circuit that converts abinary code into the desired

output signals. It is called decoder because it performs the reverse process of encoder. The

process of converting binary input code into desirable output is known as decoding.

Figure 1.24 is the logic symbol of decoder with „n‟ inputs and „m‟ outputs.

Fig:1.24. The logic symbol of decoder.

There are 2n

possible input combinations and the number of outputs (m) are less than or

equal to 2n

.Here the number of outputs can have following relation Decoder

m 2n

Digital Electronics (15EC32T)

DEPT ECE,GPT RAICHUR Page 21

BCD-to- decimal decoder

The BCD-to- decimal decoder converts each

BCD code word into one of ten possible decimal

digit indications. It is frequently referred to as a

4-line-to-10-line decoder.

Fig:1.25 logic diagram for BCD-to-decimal decoder .

TRUTH TABLE

A list of ten BCD code words and their corresponding decoding functions is given in the

truth table .Each of these decoding functions is implemented using AND gates . It is called 1:10

decoder because only 1 of 10 output lines is high . Circuit is also called BCD-decimal

converter.Each output goes HIGH only when its corresponding BCD input is applied. For

example,D6 will go HIGH only when the inputs ABCD=0110.

Digital Electronics (15EC32T)

DEPT ECE,GPT RAICHUR Page 22

Fig:1.26: BCD-to decimal decoder .

Digital Electronics (15EC32T)

DEPT ECE,GPT RAICHUR Page 23

1.29: BCD-TO SEVEN SEGMENT DECODER

Fig 1.27 (a) shows a seven segment logic symbol

Fig:1.27 : Arrangement of segments

BCD (Binary Coded Decimal) is an encoding scheme which represents each of

the decimal numbers by its equivalent 4-bit binary pattern. Seven segment displays

comprise of seven individual segments formed by either Light Emitting Diodes

(LEDs) or Liquid Crystal Displays (LCDs) arranged in a definite pattern (Fig:1.27).

For the display to work, these segments are to be driven by the certain logic

level at their input. Depending on this, seven segment displays are found to

be of two types viz., common cathode type and common anode type.

A common cathode display (Fig:1.28(a) ) has all the cathode terminals of its

LED segments tied together (green line). Further, this is grounded and hence is

considered to be at logic 0 state. This means that in order to light up an LED, one

needs to drive it high. On the other hand, a common anode display shown by

Fig:1.28(b) has all its anode terminals connected together which is further driven

high by connecting it to a positive supply voltage (green line). Hence for this kind

of display to work, one has to drive low on the cathode terminals of the individual

LED segments.

Digital Electronics (15EC32T)

DEPT ECE,GPT RAICHUR Page 24

Fig: 1.28: (a) Common cathode type display (b) Common anode type display

BCD to seven segment decoder is a circuit used to convert the input BCD

into a form suitable for the display. It has four input lines (A, B, C and D) and 7

output lines (a, b, c, d, e, f and g) as shown in Figure 1.29. Considering common

cathode type of arrangement, the truth table for the decoder can be given as in

Table.

Fig: 1.29 : BCD –to- seven segment decoder

Truth table for common cathode type BCD to seven segment decoder

Digital Electronics (15EC32T)

DEPT ECE,GPT RAICHUR Page 25

(a) Logic symbol

(b) Truth table

Fig: 1.27: BCD-TO SEVEN SEGMENT DECODER

1.30 : Decoder Ics and their features

(A) Features and Electrical characteristics of 74LS138 (3-line-to-8-Line)Decoder.

Designed specifically for high speed

Incorporates three enable pins to simplify cascading

De-multiplexing capability

Schottky clamped for high performance

ESD protection

Balanced propagation delays

Inputs accept voltages higher than VCC

Supply voltage: 1.0V to 5.5V

Typical propagation delay: 21nS

Low power consumption: 32mW

Operating temperature: -40ºC to +125ºC

Digital Electronics (15EC32T)

DEPT ECE,GPT RAICHUR Page 26

(B) Features of IC74154 (4-line-to-16-Line Decoder) :-

• Decodes 4 binary-coded inputs into one of 16 mutually exclusive outputs

• Performs the demultiplexing function by distributing data from one input line to

any one of 16 outputs

• Input clamping diodes simplify system design

• High fan-out, low-impedance, totem-pole outputs

• Typical propagation delay 3 levels of logic 23 ns Strobe 19 ns

• Typical power dissipation 45 mW

Related Documents