1 ITRS Winter Conference 2007 Makuhara, Japan International Technology Roadmap for Semiconductors 2007 ITRS ORTC [12/5 Makuhari Japan ITRS Public Conference] A.Allan, Rev 0.0 (For IRC Review) 10/29/07

Welcome message from author

This document is posted to help you gain knowledge. Please leave a comment to let me know what you think about it! Share it to your friends and learn new things together.

Transcript

1

ITRS Winter Conference 2007 Makuhara, Japan

International Technology Roadmap for Semiconductors

2007 ITRS ORTC[12/5 Makuhari Japan ITRS Public Conference]

A.Allan, Rev 0.0 (For IRC Review) 10/29/07

2

ITRS Winter Conference 2007 Makuhara, Japan

Agenda• Moore’s Law and More• Definitions• Technology Trends Update• Models Update

– ITRS Function Size Models– ITRS Functions/Chip Models– ITRS Chip Size Models

• ITRS Technology Demand Tracking [SICAS]• Summary

3

ITRS Winter Conference 2007 Makuhara, Japan

Moore’s Law & MoreMore than Moore: Diversification

Mor

e M

oore

: M

inia

turiz

atio

nM

ore

Moo

re:

Min

iatu

rizat

ion

Combining SoC and SiP: Higher Value SystemsBas

elin

e C

MO

S: C

PU, M

emor

y, L

ogic

BiochipsSensorsActuators

HVPowerAnalog/RF Passives

130nm

90nm

65nm

45nm

32nm

22nm...V

130nm

90nm

65nm

45nm

32nm

22nm...V

Information Processing

Digital contentSystem-on-chip

(SoC)

Interacting with people and environment

Non-digital contentSystem-in-package

(SiP)

Beyond CMOS

2007 ITRS Executive Summary Fig 5[updated for 2007]

Traditional ORTC Models

[Geo

met

rical

& E

quiv

alen

t sca

ling]

Scal

ing

(Mor

e M

oore

)Functional Diversification (More than Moore)

[2007 –add Definitions;Update Graphic]

Continuing SoC and SiP: Higher Value Systems

HVPower Passives

4

ITRS Winter Conference 2007 Makuhara, Japan

2007 ITRS “Moore’s Law and More”Alternative Definition Graphic

Computing &Data Storage

Heterogeneous IntegrationSystem on Chip (SOC) and System In Package (SIP)

Sense, interact, Empower

BaselineCMOS Memory RF HV

PowerPassives Sensors,

ActuatorsBio-chips,Fluidics

“More Moore”

“More than Moore”

Source: ITRS, European Nanoelectronics Initiative Advisory Council (ENIAC)

5

ITRS Winter Conference 2007 Makuhara, Japan

PIDS/FEP - Simplified Transistor Roadmap[Examples of “Equivalent Scaling” from ITRS PIDS/FEP TWGs]

65nm 45nm 32nm 22nm

PDSOI FDSOI

bulk

stressors + substrateengineering

+ high µmaterials

MuGFETMuCFET

elec

tros

tatic

con

trol

SiON

poly

high k

metal

gate stack

planar 3D

Source: ITRS, European Nanoelectronics Initiative Advisory Council (ENIAC)[ ITRS DRAM/MPU Timing: 2007/7.5 2010 2013 2016 ]

6

ITRS Winter Conference 2007 Makuhara, Japan

1. Scaling (“More Moore”)a. Geometrical (constant field) Scaling refers to the continued shrinking of

horizontal and vertical physical feature sizes of the on-chip logic and memory storage functions in order to improve density (cost per function reduction) and performance (speed, power) and reliability values to the applications and end customers.

b. Equivalent Scaling which occurs in conjunction with, and also enables, continued Geometrical Scaling, refers to 3-dimensional device structure (“Design Factor”) Improvements plus other non-geometrical process techniques and new materials that affect the electrical performance of the chip.

2. Functional Diversification (“More than Moore”)Functional Diversification refers to the incorporation into devices of functionalities that do not necessarily scale according to "Moore's Law," but provide additional value to the end customer in different ways. The "More-than-Moore" approach typically allows for the non-digital functionalities (e.g.RF communication, power control, passive components, sensors, actuators) to migrate from the system board-level into a particular package-level (SiP) or chip-level (SoC) potential solution.

2007 ITRS Definitions: “More Moore” and “More than Moore”

7

ITRS Winter Conference 2007 Makuhara, Japan

2007 Definition of the Half Pitch - unchanged[No single-product “node” designation; DRAM half-pitch still litho driver; however,

other product technology trends may be drivers on individual TWG tables]

Poly Pitch

Typical flash Un-contacted Poly

FLASH Poly Silicon ½ Pitch = Flash Poly Pitch/2

8-16 Lines

Metal Pitch

Typical DRAM/MPU/ASIC Metal Bit Line

DRAM ½ Pitch = DRAM Metal Pitch/2

MPU/ASIC M1 ½ Pitch = MPU/ASIC M1 Pitch/2

Source: 2005 ITRS - Exec. Summary Fig 2

8

ITRS Winter Conference 2007 Makuhara, Japan

Production Ramp-up Model and Technology Cycle TimingVo

lum

e (P

arts

/Mon

th)

1K

10K

100K

Months0-24

1M

10M

100M

AlphaTool

12 24-12

Development Production

BetaTool

ProductionTool

First Conf.

Papers

First Two CompaniesReaching

Production Volu

me

(Waf

ers/

Mon

th)

2

20

200

2K

20K

200K

Source: 2005 ITRS - Exec. Summary Fig 3

Fig 3 2007 - Unchanged

9

ITRS Winter Conference 2007 Makuhara, Japan

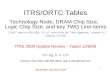

ORTC Overview – 2007 ITRS• ORTC Table 1a,b - Flash Poly (Un-contacted dense lines)

– 2-year Technology Cycle* (0.5x/4yrs) Extended to 2008– 180nm/2000; 130nm/2002; 90nm/2004; 65nm/2006; 45nm pull-in to 2008– Then return to 3-year Technology Cycle* 2 years ahead of DRAM ’08-’22

• DRAM M1 will NO LONGER be the standard TWG table technology header**– 2007 ITRS Update DRAM 3-year cycle stagger-contacted Unchanged, – However, Bits/chip delayed 1yr; 6f2 2006-2022; 56% Area Efficiency pull-in 2 yrs

• ORTC Table 1a,b - MPU/ASIC M1 Half-Pitch Trend Unchanged– Stagger-contacted, same as DRAM– 2.5-year Technology Cycle* (.5x/5yrs)– 180nm/2000; 90nm/2005; 45nm/2010(equal DRAM)– Then continue on a 3-year Technology Cycle*, equal to DRAM 2010-2020

• ORTC Table 1a,b – MPU/ASIC Printed Gate Length per FEP and Litho TWG ratio relationship to Final Physical Gate Length

– 2005 ITRS target for (3-year cycle* after 2005 Unchanged.• **TWG table Product-specific technology trend driver header items, as required by

TWGS, will be added in 2007 to individual TWG tables from ORTC Table 1a&b• Chip Size/Function Size/Density Models [Logic Gate; SRAM Cell; Dram Cell; Flash

Cell (SLC, MLC)] are updated and aligned to the latest DRAM and Flash proposals– Products: Flash; DRAM; High Performance (hp) MPU; Cost Perf. (cp) MPU; hp ASIC

*Note: Cycle = time to 0.5xlinear scaling every two

cycle periods ~ 0.71x/ cycle

Summary ofUpdates

10

ITRS Winter Conference 2007 Makuhara, Japan

2005 ITRS Flash Poly Half-Pitch Technology: 2.0-year cycle until 2yrs ahead of DRAM @ 45nm/’08

3-Year Technology Cycle2-Year Technology Cycle [’98-’06 ]

Year of Production

Technology -UncontactedPoly H-P (nm)

2003 20052001

65 223245 16

2008

20062002[Actual]

20042000[Actual]

9013018076107151 5057 13

201520122009 2018

201620132010 2019 2020

2005 ITRS MPU M1 Half-Pitch Technology: 2.5-year cycle; then equal DRAM @45nm/2010

Year of Production

Technology- ContactedM1 H-P (nm)

157 136 119 103 78 68 59 52

201620132010 2019[July’08][July’02] 20052000

201820152012 2020

[130]180 [ 65]90 2232 1645

2008200620032001 2002 2004 2007 2009

2.5-Year Technology Cycle3-2-Yr Cycle] 3-Year Technology Cycle

14

2007 (’07-’22) ITRS Technology Trends DRAM M1 Half-Pitch : 3-year cycle

3-Year Technology Cycle2-Year Technology Cycle [‘98-’04]

Year of Production

Technology - ContactedM1 H-P (nm)

201820152012 2020

201620132010 2019

2003 20052001

65 223245 16

20082006 2009

20072002[Actual]

20042000[Actual]

9013018080107151 71 57 50 14

Updated

2022

11

2022

11

2022

10’07 ‘08 ’09 ’10 ’11 ’14 ‘17 ‘20

IS: 53 45 40 36 32 22 16 11

11

ITRS Winter Conference 2007 Makuhara, Japan

2007 ITRS Product Technology Trends - Half-Pitch, Gate-Length

1.0

10.0

100.0

1000.0

1995 2000 2005 2010 2015 2020 2025

Year of Production

Prod

uct H

alf-P

itch,

Gat

e-Le

ngth

(nm

)

DRAM M1 1/2 Pitch

MPU M1 1/2 Pitch(2.5-year cycle)

Flash Poly 1/2 Pitch

MPU Gate Length -Printed

MPUGate Length -Physical

MPU M1.71X/2.5YR

Nanotechnology (<100nm) Era Begins -1999

GLpr IS =1.6818 x GLph

2007 - 2022 ITRS Range

MPU & DRAM M1& Flash Poly

.71X/3YR

Flash Poly.71X/2YR

Gate Length.71X/3YR

Before 1998.71X/3YR

After 1998.71X/2YR

Figure 8 ITRS Product Technology Trends

Past Future

plus extend all to 2022]

[DRAM &,MPU Unchanged;

[Flash 2-yr cycle extended]

Flash 2YRExtended

12

ITRS Winter Conference 2007 Makuhara, Japan

2007 ITRS Product Function Size Trends - Cell Size, Logic Gate(4t) Size

1.E-04

1.E-03

1.E-02

1.E-01

1.E+00

1.E+01

2000 2005 2010 2015 2020 2025

Year of Production

Cel

l, Lo

gic

Gat

e Si

ze(u

m2

)

DRAM Cell Size (u2)

MPU SRAM Cell Size(6t)(u2)

MPU Gate Size(4t)(u2)

Flash Cell Size (u2)SLC

Flash Eqv.bit Size(u2)2bit MLC

Flash Eqv.bit Size(u2)4bit MLC - New

Figure 9 ITRS Product Function Size [changes to DRAM and Flash;plus extend all to 2022]

Flash: 4f2 LastDesign Physical AreaFactor Improvement

DRAM: 6f2 is lastDesign Area

Factor Improvement

Logic Gate: NODesign Area

Factor Improvement(Only Scaling)

SRAM: gradualDesign Area

Factor Improvement

Flash: (MLC @ 2 bits/cell =2f2 Equivalent Area Factor)

Flash 4 bits/cell1f2 Beginning 2010

(@ 2 MLC bits/physical cell area)

(@ 4 MLC bits/physical cell area)

DRAM 6f2Pull-in to ‘06

Flash cell areaReduced due to

2YR cycleExtension

2007 - 2022 ITRS Range

Past Future

13

ITRS Winter Conference 2007 Makuhara, Japan

2007 ITRS Product Technology Trends - Functions per Chip

1.E-06

1.E-05

1.E-04

1.E-03

1.E-02

1.E-01

1.E+00

1.E+01

1.E+02

1.E+03

1970 1975 1980 1985 1990 1995 2000 2005 2010 2015 2020 2025

Year of Production

Prod

uct F

unct

ions

/Chi

p[ G

iga

(10^

9) -

bits

, tra

nsis

tors

]

Flash Bits/Chip (Gbits) Multi-Level-Cell (4bit MLC)Flash Bits/Chip (Gbits) Multi-Level-Cell (2bit MLC)Flash Bits/Chip (Gbits) Single-Level-Cell (SLC )DRAM Bits/Chip (Gbits)

MPU GTransistors/Chip - high-performance (hp)MPU GTransistors/Chip - cost-performanc (cp)

Chip Size Trends – 2007 ITRS Functions/Chip Model

Past Future2007 - 2022 ITRS Range

(@Volume Production, Affordable Chip Size**)

** Affordable Production

Chip Size Targets:DRAM, Flash < 145mm2

hp MPU < 310mm2

cp MPU < 140mm2

** Example Chip Size Targets:1.1Gt P07h MPU

@ intro in 2004/620mm2

@ prod in 2007/310mm2

** Example Chip Size Targets:0.39Gt P07c MPU

@ intro in 2004/280mm2

@ prod in 2007/140mm2

MPU ahead or =“Moore’s Law”2x Xstors/chipPer 2 years Thru 2010

Average Industry"Moores Law“ :

2x Functions/chip Per 2 Years

14

ITRS Winter Conference 2007 Makuhara, Japan

Figure 10 ITRS Product Functions per Chip

Average Industry"Moores Law“ :

2x Functions/chip Per 2 Years

2007 ITRS Product Technology Trends - Functions per Chip

1.E-02

1.E-01

1.E+00

1.E+01

1.E+02

1.E+03

1995 2000 2005 2010 2015 2020 2025

Year of Production

Prod

uct F

unct

ions

/Chi

p[ G

iga

(10^

9) -

bits

, tra

nsis

tors

]

Flash Bits/Chip (Gbits)Multi-Level-Cell (4bitMLC)

Flash Bits/Chip (Gbits)Multi-Level-Cell (2bitMLC)

Flash Bits/Chip (Gbits)Single-Level-Cell (SLC )

DRAM Bits/Chip (Gbits)

MPU GTransistors/Chip- high-performance (hp)

MPU GTransistors/Chip- cost-performanc (cp)

2007 - 2022 ITRS Range

Past Future

DRAM Bits/chip

1-yearDelay;

Flash MLC 4 bits/chip

Added

Flash SLCBits/chip

for 1-year Pull-in

[DRAM and Flash Updated]

15

ITRS Winter Conference 2007 Makuhara, Japan

0

100

200

300

400

500

600

700

1995 1998 2001 2004 2007 2010 2013 2016 2019 2022 2025

Year of Introduction and Production

(mm

2) DRAM Introduction Chip Size

Sawada Production Chip Size IS

4 chips per Litho Field @ 572mm2 = 143mm2

(22x6.5)

4G 8G 32G 64G16G

Bits/chip: 128G64M

Bits/chip:

256M

128G1G 2G

4G

8G 32G 64G

16G

256G 1T

512M

5 chips per Litho Field @ 704mm2 = 141mm2

(22x6.4)

128M

32G

16G

4G

8G

2G

32G

16G

64G2G

DRAM Des. Factor: 8.0 6.011 8.0 8.0 8.0 6.0 6.0 6.06.011 6.0 6.0

DRAM

Max Litho Field 2005 ITRS (4x) : 834mm2 (26x32)

Prod Cell Area Efficiency (CAE) = 63%-56%

Intro Cell Area Efficiency (CAE) = 73%-75%

DRAM M1 HP: 90 64 45 22 1632 11 8128180255360

2 C

hips

per

Max

Lith

o Fi

eld

2005

ITR

S (4

x):

417m

2 (2

6x16

)

Past Future 2007 - 2022 ITRS Range

Chip Size Trends – 2005 ITRS DRAM Model – UpdatedUpdated

2007 - extend to 2022; plus:

DRAM chip size shrinks Due to one-year bits/chip generation Delay;

6.0

16G @ 568

16

ITRS Winter Conference 2007 Makuhara, Japan

Past Future 2007 - 2022 ITRS Range

2005 Proposal ITRS Flash chip Size (NEW) Model (Allan)(Rev 1K, 06/23/05)

0

100

200

300

400

500

600

700

1995 1998 2001 2004 2007 2010 2013 2016 2019 2022 2025

Year of Introduction and Production

(mm

2)

Flash SLC Production Chip Size

4 chips per Max Affordable Litho Field @

572mm2 = 143mm2 (22x6.5)

Flash Prod Cell Area Efficiency (CAE) = 67%

Flash Intro Cell Area Efficiency (CAE) =TBD -

no model

5 chips per Max Affordable Litho Field @

704mm2 = 141mm2 (22x6.4)

FlashBits/chip: 4G 8G 16G 32G 64G 128G256M 1G64M 2G

16 4.032 8.0 4.0 4.0 4.0 4.0 4.04.0 Flash SLC Des.Factor: 4.0 4.0

128180255360Flash: 90 64 45 22 1632 11 8WAS/IS: 128180255360

8.0 6.011 8.0 8.0 8.0 6.0 6.0 6.06.011 6.0 6.0

90 64 45 22 1632 11 8

DRAM HP

DRAM Des. Factor:

2005:Chip Size Trends – 2005 ITRS Flash Model - Updated[2007 - extend to 2022]

Pull-in 1yr & Shrink

6.0

17

ITRS Winter Conference 2007 Makuhara, Japan

0

100

200

300

400

500

600

700

1995 1998 2001 2004 2007 2010 2013 2016 2019 2022 2025

Year of Introduction and Production

(mm

2)

MPU hp Production Chip SizeMPU cp Production Chip SizeMPU hp Introduction Chip SizeMPU cp Introduction Chip Size

DRAM M1 HP: 90 64 45 22 1632 11 8128180255360

90 68 45 22 1632 11 8MPU: 136180255360

8G

SRAM Cell Efficiency= 60%Logic Gate Efficiency = 50%

p13c1.5Bt

p16c3.1

p19c p22c

800

Max Litho Field 2005 ITRS (4x): 834mm2 (26x32)

p07h1.1Bt

p10h2.2Bt

p07h

1.1Bt

p16h p19h p22hp10h

2.2Bt

p13h

4.4Bt

p02h276Mt

p00h138Mt

p98h69Mt

p04h552Mt

p10c768Mt

hp MPU = 82% SRAM Transistors, 18% Core Logic Transistors

cp MPU = 58% SRAM Transistors, 42% Core Logic Transistors

p02h

276Mt

p04h

552Mt

26% / 2yrsChip Size Growth

p04c192Mt

p02c96Mt

p00c48Mt

p07c384Mt

p07c386Mt

p10c773Mt

p04c192Mt

p02c96Mt

p00c48Mt

p13c1.5Bt

Affordable hp MPU prod Target: 310mm2

Affordable cp MPU prod Target: 140mm2

[2.5yr Technology Cycle 2000-2010]

2 C

hips

per

Max

Lith

o Fi

eld

2005

ITR

S (4

x):

417m

2 (2

6x16

)

Chip Size Trends – 2005 ITRS MPU Model - unchanged[2007 - extend to 2022]

Past Future 2007 - 2022 ITRS Range

p25c

p25h

P22c12.4Bt

P22h35.4Bt

386Mt

773Mt

P22c12.4Bt

18

ITRS Winter Conference 2007 Makuhara, Japan

2007 “Fig 4” Technology Cycle Timing Compared to Actual Wafer Production Technology Capacity Distribution

2010

W.P.C.= Total Worldwide Wafer Production Capacity* Sources:SICAS

0.01

0.1

1

10

200420032002

W.P.C

1997

W.P.C

1998

W.P.C

1999

W.P.C

2000

W.P.C

2001

W.P.C W.P.C

2005 2006 2007

W.P.C W.P.C W.P.C W.P.C

>0.7μm

0.7-0.4μm

0.4-0.3μm

0.3- 0.2μm

0.2- 0.16μm

<0.12μm

0.16-.12μm

Feat

ure

Siz

e (H

alf P

itch)

(μm

)

Year1997 1998 1999 2000 2001 2002 2003 2004 2005 2006 2007

W.P.C = Total Worldwide Wafer Production Capacity; Source: SICAS*

- - - -

2-Year Cycle 3-Yr Cycle3-Year Cycle

= 2005/06 ITRS DRAM Contacted M1 Half-Pitch Actual= 2007 ITRS DRAM Contacted M1 Half-Pitch Target= 2007 ITRS Flash Uncontacted Poly Half Pitch Target

2007 ITRSMPU/ASIC

(2.5-yr Cycle)

SIA/SICAS Data**: 1-yr

delay from ITRS Cycle

Timingto >20% of MOS IC Capacity

[UpdatedThrough

2Q07]

** Source: The data for the graphical analysis were supplied by the Semiconductor Industry Association (SIA) from their Semiconductor Industry Capacity Statistics (SICAS). The SICAS data is collected from worldwide semiconductor manufacturers (estimated >90% of Total MOS Capacity) and published by the Semiconductor Industry Association (SIA), as of August, 2007. The detailed data are available to the public online at the SIA website, http://www.sia-online.org/pre_stat.cfm .

Note: The wafer production capacity data are plotted from the Semiconductor Industry Association (SIA) Semiconductor Industry CapacityStatistics (SICAS) 4Q data for each year, except 2Q data for 2007.The width of each of the production capacity bar corresponds to the MOS IC production start silicon area for that rangeof the feature size (y-axis). Data are based upon capacity if fully utilized.

127nm

180nm

255nm

360nm

510nm

720nm

90nm

ITRSTechnology

Cycle

Note: Includes<80nm split-out (ITRS 65nm) to be addedIn the 2008ITRS Upcate

19

ITRS Winter Conference 2007 Makuhara, Japan

MOS Capacity by Dimensions

0%

20%

40%

60%

80%

100%

3Q04

4Q04

1Q05

2Q05

3Q05

4Q05

1Q06

2Q06

3Q06

4Q06

1Q07

2Q07

WSp

W x

1000

>=0.7µ

<0.7µ >=0.4µ

<0.4µ >=0.3µ

<0.3µ >=0.2µ

<0.2µ >=0.16µ

<0.16µ

<0.16µ >=0.12µ

<0.12µ

Will Capacity Demand Remain On A 2-Year Technology Cycle (.71) for <0.8u (65nm)?[SICAS Survey November results needed for 2008 Update]

2Q05-2Q07 ~22% of Total?4Q04-4Q06 ~40% of Total

0.70

70.

707[90nm]

[65nm]

[130nm]

[n-1]

[n]

[n-2]

Source: SIA/SICAS Report: www.sia-online.org/pre_statistics.cfm

2-yrs to >20% of Total MOS for 0.71x Technology Reduction Cycle

?

<0.8?

SICAS split-outAvailableNov’07

20

ITRS Winter Conference 2007 Makuhara, Japan

MOS Capacity by Wafer-size

0.0200.0400.0600.0800.0

1000.01200.01400.01600.01800.02000.0

3Q04

4Q04

1Q05

2Q05

3Q05

4Q05

1Q06

2Q06

3Q06

4Q06

1Q07

2Q07

WSp

W x

1000

(8 in

ch e

quiv

alen

ts)

1Q 4Q3Q2Q2006

1Q 32Q200

1Q 4Q3Q2Q2004

1Q 4Q3Q2Q2005

1Q 4Q3Q2Q2003

71%YoY

1Q 4Q1997

Waf

er S

tart

s

per W

eek

(1K

)

362.7[44%]

821.4[100%]

277.4[38%]

728.2[100%]

17.4%YoY

43.0%YoY

Source: SIA/SICAS Report: www.sia-online.org

1Q07: 300mm = 33% of Total MOS200mm = 56% of Total MOS<200mm = 11% of Total MOS

SICAS 300mm MOS Capacity By Wafer SizeTracking – 3Q07 Update:[Total MOS only – 8” Equivalent] 11.8%

CAGR

2000

1000

0

<200mm

200mm

300mm

12.5%YoY

300mm/1Q04(3yrs after Intro)

200mm/1Q97SICAS Tracking Begins(6yrs after Intro)

1991->2001: 10 years intro->introWafer Generation

21

ITRS Winter Conference 2007 Makuhara, Japan

ORTC Summary – 2007 Renewal• Flash Model un-contacted poly half-pitch Extended on 2-year cycle* to 2

years ahead of DRAM (contacted) in 2008, then 3-year cycle*.• DRAM Model stagger-contacted M1 half-pitch unchanged from 2005 ITRS (3-

year cycle* after 2004), however Bits/Chip shifted by one year; 6f2/2006-22• MPU M1 stagger-contact half-pitch unchanged on a 2.5-year cycle* through

2010/45nm, then 3-year cycle*.• Printed MPU/ASIC Gate Length FEP and Litho TWGs ratio agreement, and

Physical GL targets are both unchanged and on 3-year cycle* beginning 2005.• New 2007 “Moore’s Law and More” Definitions :

– “Moore’s Law” (typically digital computing) Functional and Performance scaling is enabled by both “Geometrical” and also “Equivalent” scaling technologies

– “Functional diversification” (typically non-digital sensing, interacting) system board-level migration/miniaturization is enabled by system-in-package and system-on-chip

• Total MOS Capacity (SICAS) has been growing ~12% CAGR (SICAS), and 300mm Capacity Demand has ramped to 33% of Total MOS.

• Historical unchanged chip size models have been updated & “connected” to latest Product scaling rate model proposals, and include design factors, function size, and array efficiency targets

• The average of the industry product “Moore’s Law” (2x/chip per 2 years) continues to be met throughout the latest 2007-2022 ITRS timeframe

[* ITRS Cycle definition = time to .5x linear scaling every two cycle periods]• Industry Technology Capacity (SICAS) [3Q07 published status] continues on a

on 2-year cycle rate at the leading edge.

[plus lower Area efficiency 56% pull-in 2 years]

22

ITRS Winter Conference 2007 Makuhara, Japan

MOS Capacity by Dimensions

0.0200.0400.0600.0800.0

1000.01200.01400.01600.01800.02000.0

3Q04

4Q04

1Q05

2Q05

3Q05

4Q05

1Q06

2Q06

3Q06

4Q06

1Q07

2Q07

WSp

W x

1000

>=0.7µ

<0.7µ >=0.4µ

<0.4µ >=0.3µ

<0.3µ >=0.2µ

<0.2µ >=0.16µ

<0.16µ

<0.16µ >=0.12µ

<0.12µ

13.5% CAGR 60.6% CAGR

MOS Capacity by Dimensions

0%

20%

40%

60%

80%

100%

3Q04

4Q04

1Q05

2Q05

3Q05

4Q05

1Q06

2Q06

3Q06

4Q06

1Q07

2Q07

WSp

W x

1000

>=0.7µ

<0.7µ >=0.4µ

<0.4µ >=0.3µ

<0.3µ >=0.2µ

<0.2µ >=0.16µ

<0.16µ

<0.16µ >=0.12µ

<0.12µ

4Q04-4Q06 ~40% of Total

Source: SIA/SICAS Report: www.sia-online.org/pre_statistics.cfm

Related Documents