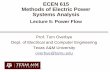

Design Example Sample final exam Problem 2 with solution (posted on D2L) ECEN5817 Lecture 43 C leg = 400 pF 250 V < V g < 350 V V = 42 V Obtain ZVS for 300 W < P load < 1 kW f s = 400 kHz Design the converter, i.e., specify n, L c , find minimum and maximum of the control input Minimize the wors-case value of the transformer primary RMS current ECEN 5817 1

Welcome message from author

This document is posted to help you gain knowledge. Please leave a comment to let me know what you think about it! Share it to your friends and learn new things together.

Transcript

-

Design ExampleSample final exam Problem 2 with solution (posted on D2L)

ECEN5817 Lecture 43

Cleg = 400 pF

250 V < Vg < 350 V

V = 42 V

Obtain ZVS for 300 W < Pload < 1 kWfs = 400 kHz

Design the converter, i.e., specify n, Lc, find minimum and maximum of the control input Minimize the wors-case value of the transformer primary RMS current

ECEN 58171

-

correction

VnVg

VnVg

VnVg

ECEN 58172

-

ECEN 58173

-

Corrected Pzvt(J) calculation on the next page

ECEN 58174

-

ZVT analysis and design example

S ifi i i h iSpecifications Design choicesVgmin 250 n 0.5Vgmax 350 Jmin 1.01V 42Pmax 1000Pmin 300Pmin 300Cleg 4.00E‐10fs 4.00E+05Imax 23.81Imin 7.14

CalculationsRo 98.98Lc 7.84E‐06f0 2.01E+06F 0.199F 0.199

Operating point 1 2 3 4Vg 250 350 250 350I 7.14 7.14 23.81 23.81J 1.41 1.01 4.71 3.37M 0.336 0.240 0.336 0.240Pzvt(J) ‐0.906 ‐0.664 ‐3.001 ‐2.144max M 0.820 0.868 0.403 0.573phi 0.516 0.372 0.933 0.667Ic rms (approx) 3.57 3.57 11.90 11.90

Corrected Pzvt(J)

ECEN 58175

Ic rms (exact) 3.50 3.48 11.83 11.79

-

Corrected Pzvt(J) calculation on the

ECEN 58176

next page

-

ZVT analysis and design example

Specifications Design choicesSpecifications Design choicesVgmin 250 n 0.33Vgmax 350 Jmin 1.01V 42Pmax 1000Pmin 300 Design improvement:g pCleg 4.00E‐10 Reduction of switching frequency by 50%fs 2.00E+05 Same MOSFETImax 23.81 Allows reduction of turns ratio to 1/3Imin 7.14 Reduced RMS currents

CalculationsRo 149.9697Lc 1.80E‐05f0 1.33E+06F 0.151

Operating point 1 2 3 4Vg 250 350 250 350I 7.14 7.14 23.81 23.81J 1.41 1.01 4.71 3.37M 0.509 0.364 0.509 0.364Pzvt(J) ‐0.906 ‐0.664 ‐3.001 ‐2.144max M 0.863 0.900 0.548 0.677phi 0.646 0.464 0.961 0.687Ic rms (approx) 2.36 2.36 7.86 7.86I ( t) 2 32 2 31 7 82 7 80

Corrected Pzvt(J)

ECEN 58177

Ic rms (exact) 2.32 2.31 7.82 7.80

-

Corrected Pzvt(J) calculation on the next page

ECEN 58178

-

ZVT analysis and design example

Specifications Design choicesVgmin 250 n 0.25Vgmax 350 Jmin 1.01V 42Pmax 1000Pmin 300 Design improvement:Cleg 1.00E‐10 Original swithcing frequencyfs 4.00E+05 Better MOSFET having reduced Cds: 100 pFImax 23.81 Allows reduction of turns ratio to 1/4Imin 7.14 Reduced RMS currents

CalculationsRo 197.96Lc 7.84E‐06f0 4.02E+06F 0 100F 0.100

Operating point 1 2 3 4Vg 250 350 250 350I 7.14 7.14 23.81 23.81J 1 41 1 01 4 71 3 37J 1.41 1.01 4.71 3.37M 0.672 0.480 0.672 0.480Pzvt(J) ‐0.906 ‐0.664 ‐3.001 ‐2.144max M 0.910 0.934 0.701 0.787phi 0.762 0.546 0.971 0.693Ic rms (approx) 1 79 1 79 5 95 5 95

Corrected Pzvt(J)

ECEN 58179

Ic rms (approx) 1.79 1.79 5.95 5.95Ic rms (exact) 1.77 1.76 5.93 5.92

-

“DC Transformer” DCX

Ultimate switched-mode power converter:

• Minimum possible voltage and current stresses on all components

• Zero-voltage switching of all semiconductor devices

It is possible to approach the above by restricting the conversion ratio to a single value, V/Vg = const., which leads to the “DC transformer” or “DCX” or , g ,“unregulated DC-DC” concept

DCX realizations

• Any hard switched or soft switched converter (e g ZVT) operated at constant• Any hard-switched or soft-switched converter (e.g. ZVT) operated at constant control (duty ratio or phase shift), optimized for a single conversion ratio

• Single-ratio converters by design

Outline:

• Introduction to DCX, dual-active-bridge DCX realization example

• Application examples

ECEN 581710

• Application examples

-

DCX derivation: basic idea

+

Vg V+–

_

ECEN 581711

-

DCX derivation: dual-active-bridge converter*

Q1 Q3 Q5 Q7 +

Vg V+–

v2 v4 v6 v81:n

Q2 Q4 Q6 Q8

_

ECEN 581712

* R.W.A.A. De Doncker, D.M. Divan, M.H. Kheraluwala, "A Three-phase Soft-Switched High-Power-Density DC-DC Converter for High-Power Applications," IEEE Tran. on Industry Applications, Jan/Feb 1991, Vol. 27, No. 1, pp. 63-73.

-

DCX (V/nVg = 1) waveforms neglecting resonant transitions

V V+

Q1

v2

Q3

v4

Q5

v6

Q7

v8

+

1:nLl

+ +

io

il

Vg V–

Q2 Q4 Q6 Q8

_

vp_

vs_

dTs/20 < d < 1Phase

shift

vp pko IdnI )1( 2

2 sg TdV

Ivs/n

22 s

l

gpk dL

I

sg dTVI

il2

s

l

gpk L

I

)1( ddTV

I sg

nioIpk

nIo

)1(2

ddnL

Il

o

Note how phase shift d controls the

ECEN 581713

o

Ts/2 Ts

shift d controls the DCX power flow

-

Dual Active Bridge (DAB) DC-DC Converter

Cp Cp Cs Cs

Q1 Q3 Q5 Q7

Ll 1:nt

io

+

–

+

–

+

–VoutCout

Q Q Q Q

ilt

Vg vp vs Rout

150-to-12 V, 100 W

Cp Cp Cs Cs

Q2 Q4 Q6 Q8

i• Zero-voltage switching of all

1 MHzEfficiency: 97.5%

ilvds6

vds2 vds4

transistors• Relatively low peak and RMS

current stressesvds2 vds4 • Circuit design trade-offs driven

by primary-side device Cp, and secondary-side device Ron

ECEN 581714

[1] D. Costinett, H. Nguyen, R. Zane, D. Maksimovic, “GaN-FET based dual active bridge DC-DC converter,” IEEE APEC 2011. [2] D. Costinett, R. Zane, D. Maksimovic, "Automatic voltage and dead time control for efficiency optimization in a dual active bridge

converter," IEEE APEC 2012.

Related Documents