© 2007 Microchip Technology Inc. DS70150C dsPIC30F6010A/6015 Data Sheet High-Performance, 16-Bit Digital Signal Controllers

Welcome message from author

This document is posted to help you gain knowledge. Please leave a comment to let me know what you think about it! Share it to your friends and learn new things together.

Transcript

Note the following details of the code protection feature on Microchip devices:

• Microchip products meet the specification contained in their particular Microchip Data Sheet.

• Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

• There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip’s Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

• Microchip is willing to work with the customer who is concerned about the integrity of their code.

• Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as “unbreakable.”

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of ourproducts. Attempts to break Microchip’s code protection feature may be a violation of the Digital Millennium Copyright Act. If such actsallow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding deviceapplications and the like is provided only for your convenienceand may be superseded by updates. It is your responsibility toensure that your application meets with your specifications.MICROCHIP MAKES NO REPRESENTATIONS ORWARRANTIES OF ANY KIND WHETHER EXPRESS ORIMPLIED, WRITTEN OR ORAL, STATUTORY OROTHERWISE, RELATED TO THE INFORMATION,INCLUDING BUT NOT LIMITED TO ITS CONDITION,QUALITY, PERFORMANCE, MERCHANTABILITY ORFITNESS FOR PURPOSE. Microchip disclaims all liabilityarising from this information and its use. Use of Microchipdevices in life support and/or safety applications is entirely atthe buyer’s risk, and the buyer agrees to defend, indemnify andhold harmless Microchip from any and all damages, claims,suits, or expenses resulting from such use. No licenses areconveyed, implicitly or otherwise, under any Microchipintellectual property rights.

DS70150C-page ii

Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Migratable Memory, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Linear Active Thermistor, Mindi, MiWi, MPASM, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2007, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

© 2007 Microchip Technology Inc.

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona, Gresham, Oregon and Mountain View, California. The Company’s quality system processes and procedures are for its PIC®

MCUs and dsPIC DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip’s quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

dsPIC30F6010A/6015

dsPIC30F6010A/6015 Enhanced Flash16-bit Digital Signal Controller (DSC)

High-Performance Modified RISC CPU:

• Modified Harvard architecture• C compiler optimized instruction set architecture

with flexible Addressing modes• 83 base instructions• 24-bit wide instructions, 16-bit wide data path

• 144 Kbytes on-chip Flash program space (Instruction words)

• 8 Kbytes of on-chip data RAM• 4 Kbytes of nonvolatile data EEPROM• Up to 30 MIPS operation:

- DC to 40 MHz external clock input- 4 MHz-10 MHz oscillator input with

PLL active (4x, 8x, 16x)- 7.37 MHz internal RC with PLL active

(4x, 8x, 16x)• 44 interrupt sources:

- 5 external interrupt sources

- 8 user selectable priority levels for each interrupt source

- 4 processor trap sources• 16 x 16-bit working register array

DSP Engine Features:

• Dual data fetch• Accumulator write-back for DSP operations

• Modulo and Bit-Reversed Addressing modes• Two, 40-bit wide accumulators with optional

saturation logic• 17-bit x 17-bit single-cycle hardware fractional/

integer multiplier• All DSP instructions single cycle• ±16-bit single-cycle shift

Peripheral Features:

• High-current sink/source I/O pins: 25 mA/25 mA

• Timer module with programmable prescaler: - Five 16-bit timers/counters; optionally pair

16-bit timers into 32-bit timer modules• 16-bit Capture input functions• 16-bit Compare/PWM output functions

• 3-wire SPI modules (supports 4 Frame modes)• I2CTM module supports Multi-Master/Slave mode

and 7-bit/10-bit addressing• 2 UART modules with FIFO Buffers• 2 CAN modules, 2.0B compliant (dsPIC306010A)

• 1 CAN module, 2.0B compliant (dsPIC306015)

Motor Control PWM Module Features:

• 8 PWM output channels:- Complementary or Independent Output

modes- Edge and Center-Aligned modes

• 4 duty cycle generators

• Dedicated time base• Programmable output polarity• Dead-Time control for Complementary mode

• Manual output control• Trigger for A/D conversions

Quadrature Encoder Interface Module Features:

• Phase A, Phase B and Index Pulse input

• 16-bit up/down position counter • Count direction status• Position Measurement (x2 and x4) mode

• Programmable digital noise filters on inputs• Alternate 16-bit Timer/Counter mode• Interrupt on position counter rollover/underflow

Note: This data sheet summarizes features of thisgroup of dsPIC30F devices and is not intended to bea complete reference source. For more informationon the CPU, peripherals, register descriptions andgeneral device functionality, refer to the “dsPIC30FFamily Reference Manual” (DS70046). For moreinformation on the device instruction set and pro-gramming, refer to the “dsPIC30F/33F ProgrammersReference Manual” (DS70157).

© 2007 Microchip Technology Inc. DS70150C-page 1

dsPIC30F6010A/6015

Analog Features:

• 10-bit Analog-to-Digital Converter (ADC) with4 S/H Inputs:- 1 Msps conversion rate

- 16 input channels- Conversion available during Sleep and Idle

• Programmable Brown-out Reset

Special Microcontroller Features:

• Enhanced Flash program memory:

- 10,000 erase/write cycle (min.) for industrial temperature range, 100K (typical)

• Data EEPROM memory:- 100,000 erase/write cycle (min.) for

industrial temperature range, 1M (typical)• Self-reprogrammable under software control

• Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

• Flexible Watchdog Timer (WDT) with on-chip, low-power RC oscillator for reliable operation

• Fail-Safe Clock Monitor operation detects clock failure and switches to on-chip, low-power RC oscillator

• Programmable code protection• In-Circuit Serial Programming™ (ICSP™)• Selectable Power Management modes

- Sleep, Idle and Alternate Clock modes

CMOS Technology:

• Low-power, high-speed Flash technology• Wide operating voltage range (2.5V to 5.5V)• Industrial and Extended temperature ranges

• Low-power consumption

dsPIC30F Motor Control and Power Conversion Family*

Device PinsProgram

Mem. Bytes/Instructions

SRAMBytes

EEPROMBytes

Timer 16-bit

InputCap

OutputComp/Std

PWM

MotorControl

PWM

A/D 10-bit 1 Msps

Quad Enc U

AR

T

SP

I

I2 C™

CA

N

dsPIC30F2010 28 12K/4K 512 1024 3 4 2 6 ch 6 ch Yes 1 1 1 —

dsPIC30F3010 28 24K/8K 1024 1024 5 4 2 6 ch 6 ch Yes 1 1 1 —

dsPIC30F4012 28 48K/16K 2048 1024 5 4 2 6 ch 6 ch Yes 1 1 1 1

dsPIC30F3011 40/44

24K/8K 1024 1024 5 4 4 6 ch 9 ch Yes 2 1 1 —

dsPIC30F4011 40/44

48K/16K 2048 1024 5 4 4 6 ch 9 ch Yes 2 1 1 1

dsPIC30F5015 64 66K/22K 2048 1024 5 4 4 8 ch 16 ch Yes 1 2 1 1

dsPIC30F5016 80 66K/22K 2048 1024 5 4 4 8 ch 16 ch Yes 1 2 1 1

dsPIC30F6010A 80 144K/48K 8192 4096 5 8 8 8 ch 16 ch Yes 2 2 1 2

dsPIC30F6015 64 144K/48K 8192 4096 5 8 8 8 ch 16 ch Yes 2 2 1 1

* This table provides a summary of the dsPIC30F peripheral features. Other available devices in the dsPIC30F Motor Control and Power Conversion Family are shown for feature comparison.

DS70150C-page 2 © 2007 Microchip Technology Inc.

dsPIC30F6010A/6015

Pin Diagram

72

74

73

71

70

69

68

67

66

65

64

63

62

61

20

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

50

49

48

47

46

45

44

21

41

4039383736353423 24 25 26 27 28 29 30 31 32 33dsPIC30F6010A

17

18

19

75

1

57

56

55

54

53

52

51

60

59

58

43

42

76

78

77

79

2280

IC5/

RD

12O

C4/

RD

3

OC

3/R

D2

EM

UD

2/O

C2/

RD

1

PW

M2L

/RE

2P

WM

1H/R

E1

PW

M1L

/RE

0

C2R

X/R

G0

C2T

X/R

G1

C1T

X/R

F1

C1R

X/R

F0

PW

M3L

/RE

4

PW

M2H

/RE

3

OC

8/U

PD

N/C

N16

/RD

7

OC

6/C

N14

/RD

5

EMUC2/OC1/RD0

IC4/RD11

IC2/RD9

IC1/RD8

INT4/RA15

IC3/RD10

INT3/RA14VSS

OSC1/CLKI

VDD

SCL/RG2

U1RX/RF2

U1TX/RF3

EMUC1/SOSCO/T1CK/CN0/RC14

EMUD1/SOSCI/CN1/RC13V

RE

F+

/RA

10

VR

EF-/

RA

9

AV

DD

AV

SS

AN

8/R

B8

AN

9/R

B9

AN

10/R

B10

AN

11/R

B11

VD

D

U2R

X/C

N17

/RF

4

IC8/

CN

21/R

D15

U2T

X/C

N18

/RF

5

AN

6/O

CFA

/RB

6

AN

7/R

B7

PWM4H/RE7

T2CK/RC1

T4CK/RC3

SCK2/CN8/RG6

SDI2/CN9/RG7

SDO2/CN10/RG8

MCLR

SS2/CN11/RG9

AN4/QEA/CN6/RB4AN3/INDX/CN5/RB3

AN2/SS1/CN4/RB2

PGC/EMUC/AN1/CN3/RB1

PGD/EMUD/AN0/CN2/RB0

VSS

VDD

PWM3H/RE5

PWM4L/RE6

FLTB/INT2/RE9

FLTA/INT1/RE8

AN

12/R

B12

AN

13/R

B13

AN

14/R

B14

AN

15/O

CF

B/C

N12

/RB

15

VD

D

VS

S

OC

5/C

N13

/RD

4

IC6/

CN

19/R

D13

SDA/RG3

SDI1/RF7

EMUD3/SDO1/RF8

AN5/QEB/CN7/RB5

VS

S

OSC2/CLKO/RC15O

C7/

CN

15/R

D6

EMUC3/SCK1/INT0/RF6

IC7/

CN

20/R

D14

80-Pin TQFP

Note: Pinout subject to change.

© 2007 Microchip Technology Inc. DS70150C-page 3

dsPIC30F6010A/6015

Pin Diagram

dsPIC30F6015

64-Pin TQFP

Note: Pinout subject to change.

12345678910111213 36

353433

32313029282726

64 63 62 61 60 59 58 57 56

141516

17 18 19 20 21 22 23 24 25

EMUC1/SOSCO/T1CK/CN0/RC14EMUD1/SOSCI/T4CK/CN1/RC13EMUC2/OC1/RD0IC4/INT4/RD11

IC2/FLTB/INT2/RD9IC1/FLTA/INT1/RD8VSS

OSC2/CLKO/RC15OSC1/CLKIVDD

SCL/RG2

EMUC3/SCK1/INT0/RF6U1RX/SDI1/RF2EMUD3/U1TX/SDO1/RF3

PWM3H/RE5PWM4L/RE6PWM4H/RE7

SCK2/CN8/RG6SDI2/CN9/RG7

SDO2/CN10/RG8MCLR

VSS

VDD

AN3/INDX/CN5/RB3AN2/SS1/CN4/RB2

AN1/VREF-/CN3/RB1AN0/VREF+/CN2/RB0

OC

8/U

PD

N/C

N16

/RD

7

PW

M3L

/RE

4P

WM

2H/R

E3

PW

M2L

/RE

2

VS

S

PW

M1L

/RE

0C

1TX

/RF

1

PW

M1H

/RE

1

EM

UD

2/O

C2/

RD

1O

C3/

RD

2

PG

C/E

MU

C/A

N6/

OC

FA/R

B6

PG

D/E

MU

D/A

N7/

RB

7A

VD

D

AV

SS

AN

8/R

B8

AN

9/R

B9

AN

10/R

B10

AN

11/R

B11

VS

S

VD

D

AN

12/R

B12

AN

13/R

B13

AN

14/R

B14

AN

15/O

CF

B/C

N12

/RB

15

U2T

X/C

N18

/RF

5U

2RX

/CN

17/R

F4

SDA/RG3

43424140393837

44

484746

50 495154 53 5255

45

SS2/CN11/RG9

AN5/QEB/IC8/CN7/RB5AN4/QEA/IC7/CN6/RB4

IC3/INT3/RD10

VD

D

C1R

X/R

F0

OC

4/R

D3

OC

7/C

N15

/RD

6O

C6/

IC6/

CN

14/R

D5

OC

5/IC

5/C

N13

/RD

4

DS70150C-page 4 © 2007 Microchip Technology Inc.

dsPIC30F6010A/6015

Table of Contents1.0 Device Overview ......................................................................................................................................................................... 72.0 CPU Architecture Overview ....................................................................................................................................................... 133.0 Memory Organization ................................................................................................................................................................ 214.0 Address Generator Units ........................................................................................................................................................... 335.0 Interrupts .................................................................................................................................................................................. 396.0 Flash Program Memory ............................................................................................................................................................. 477.0 Data EEPROM Memory ............................................................................................................................................................ 538.0 I/O Ports .................................................................................................................................................................................... 579.0 Timer1 Module .......................................................................................................................................................................... 6310.0 Timer2/3 Module ....................................................................................................................................................................... 6711.0 Timer4/5 Module ...................................................................................................................................................................... 7512.0 Input Capture Module ............................................................................................................................................................... 7913.0 Output Compare Module ........................................................................................................................................................... 8314.0 Quadrature Encoder Interface (QEI) Module ............................................................................................................................ 8715/0 Motor Control PWM Module ...................................................................................................................................................... 9316.0 SPI Module .............................................................................................................................................................................. 10317.0 I2C™ Module .......................................................................................................................................................................... 10718.0 Universal Asynchronous Receiver Transmitter (UART) Module ............................................................................................. 11519.0 CAN Module ............................................................................................................................................................................ 12320.0 10-bit High-Speed Analog-to-Digital Converter (ADC) Module ............................................................................................... 13521.0 System Integration .................................................................................................................................................................. 14722.0 Instruction Set Summary ......................................................................................................................................................... 16323.0 Development Support .............................................................................................................................................................. 17124.0 Electrical Characteristics ......................................................................................................................................................... 17525.0 Packaging Information ............................................................................................................................................................. 215Appendix A: Revision History ............................................................................................................................................................ 219Appendix B: Device Comparisons .................................................................................................................................................... 221Appendix C: Migration From dsPIC30F6010 to dsPIC30F6010A ..................................................................................................... 223Index ................................................................................................................................................................................................. 225The Microchip Web Site .................................................................................................................................................................... 231Customer Change Notification Service ............................................................................................................................................. 231Customer Support ............................................................................................................................................................................. 231Reader Response ............................................................................................................................................................................. 232Product Identification System ............................................................................................................................................................. 23

TO OUR VALUED CUSTOMERSIt is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Micro-chip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refinedand enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department viaE-mail at [email protected] or fax the Reader Response Form in the back of this data sheet to (480) 792-4150. Wewelcome your feedback.

Most Current Data SheetTo obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

ErrataAn errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for cur-rent devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revi-sion of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site; http://www.microchip.com• Your local Microchip sales office (see last page)When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you areusing.

Customer Notification SystemRegister on our web site at www.microchip.com to receive the most current information on all of our products.

© 2007 Microchip Technology Inc. DS70150C-page 5

dsPIC30F6010A/6015

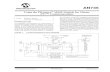

1.0 DEVICE OVERVIEW This document contains device-specific information forthe dsPIC30F6010A and dsPIC30F6015 devices. ThedsPIC30F devices contain extensive Digital SignalProcessor (DSP) functionality within a high-performance16-bit microcontroller (MCU) architecture. Figure 1-1shows a device block diagram for the dsPIC30F6010Adevice. Figure 1-2 shows a device block diagram for thedsPIC30F6015 device.

Note: This data sheet summarizes features of thisgroup of dsPIC30F devices and is not intended to bea complete reference source. For more informationon the CPU, peripherals, register descriptions andgeneral device functionality, refer to the “dsPIC30FFamily Reference Manual” (DS70046). For moreinformation on the device instruction set and pro-gramming, refer to the “dsPIC30F/33F ProgrammersReference Manual” (DS70157).

© 2007 Microchip Technology Inc. DS70150C-page 7

dsPIC30F6010A/6015

FIGURE 1-1: dsPIC30F6010A BLOCK DIAGRAM

AN8/RB8AN9/RB9AN10/RB10AN11/RB11

Power-upTimer

OscillatorStart-up Timer

POR/BORReset

WatchdogTimer

InstructionDecode &Control

OSC1/CLKI

MCLR

VDD, VSS

AN4/QEA/CN6/RB4

AN12/RB12AN13/RB13AN14/RB14AN15/OCFB/CN12/RB15

Low-VoltageDetect

UART1,SPI1, Motor Control

PWM

INT4/RA15INT3/RA14VREF+/RA10VREF-/RA9

CAN2

TimingGeneration

CAN1,

AN5/QEB/CN7/RB5

16

PCH PCLProgram Counter

ALU<16>

16

Address Latch

Program Memory(144 Kbytes)

Data Latch

24

24

24

24

X Data Bus

IR

I2C™

QEI

AN6/OCFA/RB6AN7/RB7

PCU

PWM1L/RE0PWM1H/RE1PWM2L/RE2PWM2H/RE3PWM3L/RE4

10-bit ADC

Timers

PWM3H/RE5PWM4L/RE6PWM4H/RE7FLTA/INT1/RE8FLTB/INT2/RE9

SCK2/CN8/RG6SDI2/CN9/RG7

SDO2/CN10/RG8SS2/CN11/RG9

U2TX/CN18/RF5EMUC3/SCK1/INT0/RF6SDI1/RF7EMUD3/SDO1/RF8

InputCaptureModule

Output Compare

Module

EMUC1/SOSCO/T1CK/CN0/RC14EMUD1/SOSCI/CN1/RC13T4CK/RC3T2CK/RC1

PORTB

C1RX/RF0C1TX/RF1U1RX/RF2U1TX/RF3

C2RX/RG0C2TX/RG1

SCL/RG2SDA/RG3

PORTG PORTF

PORTD

16

16 16

16 x 16W Reg Array

Divide Unit Engine

DSP

Decode

ROM Latch

16

Y Data Bus

Effective Address

X RAGUX WAGU Y AGU

PGD/EMUD/AN0/CN2/RB0PGC/EMUC/AN1/CN3/RB1AN2/SS1/CN4/RB2AN3/INDX/CN5/RB3

OSC2/CLKO/RC15

U2RX/CN17/RF4

AVDD, AVSS

UART2SPI2

16

16

16

16

16

PORTA

PORTC

PORTE

16

16

16

16

8

InterruptController PSV & Table

Data AccessControl Block

StackControl Logic

LoopControlLogic

Data LatchData LatchY Data

(4 Kbytes)RAM

X Data

(4 Kbytes)RAM

AddressLatch

AddressLatch

Control Signals to Various Blocks

EMUC2/OC1/RD0EMUD2/OC2/RD1OC3/RD2OC4/RD3OC5/CN13/RD4OC6/CN14/RD5OC7/CN15/RD6OC8/UPDN/CN16/RD7IC1/RD8IC2/RD9IC3/RD10IC4/RD11IC5/RD12IC6/CN19/RD13IC7/CN20/RD14IC8/CN21/RD15

16

Data EEPROM(4 Kbytes)

16

DS70150C-page 8 © 2007 Microchip Technology Inc.

dsPIC30F6010A/6015

FIGURE 1-2: dsPIC30F6015 BLOCK DIAGRAM

AN8/RB8AN9/RB9AN10/RB10AN11/RB11

Power-upTimer

OscillatorStart-up Timer

POR/BORReset

WatchdogTimer

InstructionDecode &Control

OSC1/CLKI

MCLR

VDD, VSS

AN4/QEA/IC7/CN6/RB4

AN12/RB12AN13/RB13AN14/RB14AN15/OCFB/CN12/RB15

Low-VoltageDetect

UART1,SPI1, Motor Control

PWM

TimingGeneration

CAN1

AN5/QEB/IC8/CN7/RB5

16

PCH PCLProgram Counter

ALU<16>

16

Address Latch

Program Memory(144 Kbytes)

Data Latch

24

24

24

24

X Data Bus

IR

I2C™

QEI

PGC/EMUC/AN6/OCFA/RB6PGD/EMUD/AN7/RB7

PCU

PWM1L/RE0PWM1H/RE1PWM2L/RE2PWM2H/RE3PWM3L/RE4

10-bit ADC

Timers

PWM3H/RE5PWM4L/RE6PWM4H/RE7

SCK2/CN8/RG6SDI2/CN9/RG7

SDO2/CN10/RG8SS2/CN11/RG9 U2TX/CN18/RF5

EMUC3/SCK1/INT0/RF6

InputCaptureModule

Output Compare

Module

EMUC1/SOSCO/T1CK/CN0/RC14EMUD1/SOSCI/T4CK/CN1/RC13

PORTB

C1RX/RF0C1TX/RF1U1RX/SDI1/RF2EMUD3/U1TX/SDO1/RF3

SCL/RG2SDA/RG3

PORTG PORTF

PORTD

16

16 16

16 x 16W Reg Array

Divide Unit Engine

DSP

Decode

ROM Latch

16

Y Data Bus

Effective Address

X RAGUX WAGU Y AGU

AN0/VREF+/CN2/RB0AN1/VREF-/CN3/RB1AN2/SS1/CN4/RB2AN3/INDX/CN5/RB3

OSC2/CLKO/RC15

U2RX/CN17/RF4

AVDD, AVSS

UART2SPI2

16

16

16

16

16

PORTC

PORTE

16

16

16

16

8

InterruptController PSV & Table

Data AccessControl Block

StackControl Logic

LoopControlLogic

Data LatchData LatchY Data

(4 Kbytes)RAM

X Data

(4 Kbytes)RAM

AddressLatch

AddressLatch

Control Signals to Various Blocks

EMUC2/OC1/RD0EMUD2/OC2/RD1OC3/RD2OC4/RD3OC5/IC5/CN13/RD4

OC7/CN15/RD6OC8/UPDN/CN16/RD7IC1/FLTA/INT1/RD8IC2/FLTB/INT2/RD9IC3/INT3/RD10IC4/INT4/RD11

16

Data EEPROM(4 Kbytes)

16

OC6/IC6/CN14/RD5

© 2007 Microchip Technology Inc. DS70150C-page 9

dsPIC30F6010A/6015

Table 1-1 provides a brief description of the device I/Opinout and the functions that are multiplexed to a portpin. Multiple functions may exist on one port pin. Whenmultiplexing occurs, the peripheral module’s functionalrequirements may force an override of the datadirection of the port pin.

TABLE 1-1: dsPIC30F6010A/6015 I/O PIN DESCRIPTIONS

Pin NamePin

TypeBuffer Type

Description

AN0-AN15 I Analog Analog input channels. AN0 and AN1 are also used for device programming data and clock inputs, respectively.

AVDD P P Positive supply for analog module.

AVSS P P Ground reference for analog module.

CLKICLKO

IO

ST/CMOS—

External clock source input. Always associated with OSC1 pin function.Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function.

CN0-CN23 I ST Input change notification inputs. Can be software programmed for internal weak pull-ups on all inputs.

C1RXC1TXC2RXC2TX

IOIO

ST—ST—

CAN1 bus receive pin.CAN1 bus transmit pin.CAN2 bus receive pin.CAN2 bus transmit pin.

EMUDEMUCEMUD1EMUC1EMUD2EMUC2EMUD3EMUC3

I/OI/OI/OI/OI/OI/OI/OI/O

STSTSTSTSTSTSTST

ICD Primary Communication Channel data input/output pin.ICD Primary Communication Channel clock input/output pin.ICD Secondary Communication Channel data input/output pin.ICD Secondary Communication Channel clock input/output pin.ICD Tertiary Communication Channel data input/output pin.ICD Tertiary Communication Channel clock input/output pin.ICD Quaternary Communication Channel data input/output pin.ICD Quaternary Communication Channel clock input/output pin.

IC1-IC8 I ST Capture inputs 1 through 8.

INDXQEA

QEB

UPDN

II

I

O

STST

ST

CMOS

Quadrature Encoder Index Pulse input.Quadrature Encoder Phase A input in QEI mode. Auxiliary Timer External Clock/Gate input in Timer mode.Quadrature Encoder Phase A input in QEI mode. Auxiliary Timer External Clock/Gate input in Timer mode.Position Up/Down Counter Direction State.

INT0INT1INT2INT3INT4

IIIII

STSTSTSTST

External interrupt 0.External interrupt 1.External interrupt 2.External interrupt 3.External interrupt 4.

Legend: CMOS = CMOS compatible input or output Analog = Analog inputST = Schmitt Trigger input with CMOS levels O = Output I = Input P = Power

DS70150C-page 10 © 2007 Microchip Technology Inc.

dsPIC30F6010A/6015

FLTAFLTBPWM1LPWM1HPWM2LPWM2HPWM3LPWM3HPWM4LPWM4H

IIOOOOOOOO

STST————————

PWM Fault A input.PWM Fault B input.PWM 1 Low output. PWM 1 High output.PWM 2 Low output.PWM 2 High output.PWM 3 Low output.PWM 3 High output.PWM 4 Low output.PWM 4 High output.

MCLR I/P ST Master Clear (Reset) input or programming voltage input. This pin is an active-low Reset to the device.

OCFAOCFBOC1-OC8

IIO

STST—

Compare Fault A input (for Compare channels 1, 2, 3 and 4).Compare Fault B input (for Compare channels 5, 6, 7 and 8).Compare outputs 1 through 8.

OSC1

OSC2

I

I/O

ST/CMOS

—

Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.

PGDPGC

I/OI

STST

In-Circuit Serial Programming™ data input/output pin.In-Circuit Serial Programming clock input pin.

RA9-RA10RA14-RA15

I/OI/O

STST

PORTA is a bidirectional I/O port.

RB0-RB15 I/O ST PORTB is a bidirectional I/O port.

RC1 RC3RC13-RC15

I/OI/OI/O

STSTST

PORTC is a bidirectional I/O port.

RD0-RD15 I/O ST PORTD is a bidirectional I/O port.

RE0-RE9 I/O ST PORTE is a bidirectional I/O port.

RF0-RF8 I/O ST PORTF is a bidirectional I/O port.

RG0-RG3RG6-RG9

I/OI/O

STST

PORTG is a bidirectional I/O port.

SCK1SDI1SDO1SS1SCK2SDI2SDO2SS2

I/OIOI

I/OIOI

STST—STSTST—ST

Synchronous serial clock input/output for SPI #1.SPI #1 Data In.SPI #1 Data Out.SPI #1 Slave Synchronization.Synchronous serial clock input/output for SPI #2.SPI #2 Data In.SPI #2 Data Out.SPI #2 Slave Synchronization.

SCLSDA

I/OI/O

STST

Synchronous serial clock input/output for I2C™.Synchronous serial data input/output for I2C.

SOSCOSOSCI

OI

—ST/CMOS

32 kHz low-power oscillator crystal output. 32 kHz low-power oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.

T1CKT2CKT4CK

III

STSTST

Timer1 external clock input.Timer2 external clock input.Timer4 external clock input.

TABLE 1-1: dsPIC30F6010A/6015 I/O PIN DESCRIPTIONS (CONTINUED)

Pin NamePin

TypeBuffer Type

Description

Legend: CMOS = CMOS compatible input or output Analog = Analog inputST = Schmitt Trigger input with CMOS levels O = Output I = Input P = Power

© 2007 Microchip Technology Inc. DS70150C-page 11

dsPIC30F6010A/6015

U1RXU1TXU1ARXU1ATXU2RXU2TX

IOIOIO

ST—ST—ST—

UART1 Receive.UART1 Transmit.UART1 Alternate Receive.UART1 Alternate Transmit.UART2 Receive.UART2 Transmit.

VDD P — Positive supply for logic and I/O pins.

VSS P — Ground reference for logic and I/O pins.

VREF+ I Analog Analog Voltage Reference (High) input.

VREF- I Analog Analog Voltage Reference (Low) input.

TABLE 1-1: dsPIC30F6010A/6015 I/O PIN DESCRIPTIONS (CONTINUED)

Pin NamePin

TypeBuffer Type

Description

Legend: CMOS = CMOS compatible input or output Analog = Analog inputST = Schmitt Trigger input with CMOS levels O = Output I = Input P = Power

DS70150C-page 12 © 2007 Microchip Technology Inc.

dsPIC30F6010A/6015

2.0 CPU ARCHITECTUREOVERVIEW

This document summarizes the CPU and peripheralfunctions of the dsPIC30F6010A/6015. For a completedescription of this functionality, please refer tothe “dsPIC30F Family Reference Manual” (DS70046).

2.1 Core Overview

The core has a 24-bit instruction word. The ProgramCounter (PC) is 23 bits wide with the Least Significantbit (LSb) always clear (see Section 3.1 “ProgramAddress Space”), and the Most Significant bit (MSb)is ignored during normal program execution, except forcertain specialized instructions. Thus, the PC canaddress up to 4M instruction words of user programspace. An instruction prefetch mechanism is used tohelp maintain throughput. Program loop constructs,free from loop count management overhead, are sup-ported using the DO and REPEAT instructions, both ofwhich are interruptible at any point.

The working register array consists of 16x16-bit regis-ters, each of which can act as data, address or offsetregisters. One working register (W15) operates as aSoftware Stack Pointer for interrupts and calls.

The data space is 64 Kbytes (32K words) and is split intotwo blocks, referred to as X and Y data memory. Eachblock has its own independent Address Generation Unit(AGU). Most instructions operate solely through the Xmemory AGU, which provides the appearance of a sin-gle unified data space. The Multiply-Accumulate (MAC)class of dual source DSP instructions operate throughboth the X and Y AGUs, splitting the data address spaceinto two parts (see Section 3.2 “Data AddressSpace”). The X and Y data space boundary is device-specific and cannot be altered by the user. Each dataword consists of 2 bytes, and most instructions canaddress data either as words or bytes.

There are two methods of accessing data stored inprogram memory:

• The upper 32 Kbytes of data space memory can be mapped into the lower half (user space) of program space at any 16K program word boundary, defined by the 8-bit Program Space Visibility Page (PSVPAG) register. This lets any instruction access program space as if it were data space, with a limita-tion that the access requires an additional cycle. Moreover, only the lower 16 bits of each instruction word can be accessed using this method.

• Linear indirect access of 32K word pages within program space is also possible using any working register, via table read and write instructions. Table read and write instructions can be used to access all 24 bits of an instruction word.

Overhead-free circular buffers (Modulo Addressing)are supported in both X and Y address spaces. This isprimarily intended to remove the loop overhead forDSP algorithms.

The X AGU also supports Bit-Reversed Addressing ondestination Effective Addresses, to greatly simplifyinput or output data reordering for radix-2 FFT algo-rithms. Refer to Section 4.0 “Address GeneratorUnits” for details on Modulo and Bit-ReversedAddressing.

The core supports Inherent (no operand), Relative, Lit-eral, Memory Direct, Register Direct, Register Indirect,Register Offset and Literal Offset Addressing modes.Instructions are associated with predefined addressingmodes, depending upon their functional requirements.

For most instructions, the core is capable of executinga data (or program data) memory read, a working reg-ister (data) read, a data memory write and a program(instruction) memory read per instruction cycle. As aresult, 3-operand instructions are supported, allowingC = A + B operations to be executed in a single cycle.

A DSP engine has been included to significantlyenhance the core arithmetic capability and throughput.It features a high-speed 17-bit by 17-bit multiplier, a40-bit ALU, two 40-bit saturating accumulators and a40-bit bidirectional barrel shifter. Data in the accumula-tor or any working register can be shifted up to 16 bitsright or 16 bits left in a single cycle. The DSP instruc-tions operate seamlessly with all other instructions andhave been designed for optimal real-time performance.The MAC class of instructions can concurrently fetchtwo data operands from memory, while multiplying twoW registers. To enable this concurrent fetching of dataoperands, the data space has been split for theseinstructions and linear for all others. This has beenachieved in a transparent and flexible manner, by ded-icating certain working registers to each address spacefor the MAC class of instructions.

The core does not support a multi-stage instructionpipeline. However, a single stage instruction prefetchmechanism is used, which accesses and partiallydecodes instructions a cycle ahead of execution, inorder to maximize available execution time. Mostinstructions execute in a single cycle, with certainexceptions.

The core features a vectored exception processingstructure for traps and interrupts, with 62 independentvectors. The exceptions consist of up to 8 traps (ofwhich 4 are reserved) and 54 interrupts. Each interruptis prioritized based on a user-assigned priority between1 and 7 (1 being the lowest priority and 7 being thehighest) in conjunction with a predetermined ‘naturalorder’. Traps have fixed priorities, ranging from 8 to 15.

Note: This data sheet summarizes features of thisgroup of dsPIC30F devices and is not intended to bea complete reference source. For more informationon the CPU, peripherals, register descriptions andgeneral device functionality, refer to the “dsPIC30FFamily Reference Manual” (DS70046). For moreinformation on the device instruction set and pro-gramming, refer to the “dsPIC30F/33F ProgrammersReference Manual” (DS70157).

© 2007 Microchip Technology Inc. DS70150C-page 13

dsPIC30F6010A/6015

2.2 Programmer’s Model

The programmer’s model is shown in Figure 2-1 andconsists of 16x16-bit working registers (W0 throughW15), 2x40-bit accumulators (AccA and AccB),STATUS register (SR), Data Table Page register(TBLPAG), Program Space Visibility Page register(PSVPAG), DO and REPEAT registers (DOSTART,DOEND, DCOUNT and RCOUNT), and ProgramCounter (PC). The working registers can act as data,address or offset registers. All registers are memorymapped. W0 acts as the W register for file registeraddressing.

Some of these registers have a shadow register asso-ciated with each of them, as shown in Figure 2-1. Theshadow register is used as a temporary holding registerand can transfer its contents to or from its host registerupon the occurrence of an event. None of the shadowregisters are accessible directly. The following rulesapply for transfer of registers into and out of shadows.

• PUSH.S and POP.S W0, W1, W2, W3, SR (DC, N, OV, Z and C bits only) are transferred.

• DO instruction DOSTART, DOEND, DCOUNT shadows are pushed on loop start and popped on loop end.

When a byte operation is performed on a workingregister, only the Least Significant Byte of the targetregister is affected. However, a benefit of memorymapped working registers is that both the Least andMost Significant Bytes can be manipulated throughbyte-wide data memory space accesses.

2.2.1 SOFTWARE STACK POINTER/ FRAME POINTER

The dsPIC® DSC devices contain a software stack.W15 is the dedicated Software Stack Pointer (SP), andwill be automatically modified by exception processingand subroutine calls and returns. However, W15 can bereferenced by any instruction in the same manner as allother W registers. This simplifies the reading, writingand manipulation of the Stack Pointer (e.g., creatingstack frames).

W15 is initialized to 0x0800 during a Reset. The usermay reprogram the SP during initialization to anylocation within data space.

W14 has been dedicated as a Stack Frame Pointer asdefined by the LNK and ULNK instructions. However,W14 can be referenced by any instruction in the samemanner as all other W registers.

2.2.2 STATUS REGISTER

The dsPIC DSC core has a 16-bit STATUS register(SR), the LSB of which is referred to as the SR LowByte (SRL) and the MSB as the SR High Byte (SRH).See Figure 2-1 for SR layout.

SRL contains all the MCU ALU operation status flags(including the Z bit), as well as the CPU Interrupt Prior-ity Level Status bits, IPL<2:0>, and the Repeat ActiveStatus bit, RA. During exception processing, SRL isconcatenated with the MSB of the PC to form acomplete word value which is then stacked.

The upper byte of the SR register contains the DSPadder/subtractor Status bits, the DO Loop Active bit(DA) and the Digit Carry (DC) Status bit.

2.2.3 PROGRAM COUNTER

The Program Counter is 23 bits wide. Bit 0 is alwaysclear. Therefore, the PC can address up to 4Minstruction words.

Note: In order to protect against misalignedstack accesses, W15<0> is always clear.

DS70150C-page 14 © 2007 Microchip Technology Inc.

dsPIC30F6010A/6015

FIGURE 2-1: dsPIC30F6010A/6015 PROGRAMMER’S MODEL

TABPAG

PC22 PC0

7 0

D0D15

Program Counter

Data Table Page Address

STATUS Register

Working Registers

DSP OperandRegisters

W1

W2

W3

W4

W5

W6

W7

W8

W9

W10

W11

W12/DSP Offset

W13/DSP Write-Back

W14/Frame Pointer

W15/Stack Pointer

DSP AddressRegisters

AD39 AD0AD31

DSPAccumulators

AccA

AccB

PSVPAG7 0

Program Space Visibility Page Address

Z

0

OA OB SA SB

RCOUNT15 0

REPEAT Loop Counter

DCOUNT15 0

DO Loop Counter

DOSTART

22 0DO Loop Start Address

IPL2 IPL1

SPLIM Stack Pointer Limit Register

AD15

SRL

PUSH.S Shadow

DO Shadow

OAB SAB

15 0 Core Configuration Register

Legend

CORCON

DA DC RA N

TBLPAG

PSVPAG

IPL0 OV

W0/WREG

SRH

DO Loop End AddressDOEND

22

C

© 2007 Microchip Technology Inc. DS70150C-page 15

dsPIC30F6010A/6015

2.3 Divide Support

The dsPIC DSC devices feature a 16/16-bit signedfractional divide operation, as well as 32/16-bit and16/16-bit signed and unsigned integer divide opera-tions, in the form of single instruction iterative divides.The following instructions and data sizes aresupported:

1. DIVF – 16/16 signed fractional divide2. DIV.sd – 32/16 signed divide3. DIV.ud – 32/16 unsigned divide

4. DIV.s – 16/16 signed divide5. DIV.u – 16/16 unsigned divide

The divide instructions must be executed within aREPEAT loop. Any other form of execution (e.g., aseries of discrete divide instructions) will not functioncorrectly because the instruction flow depends onRCOUNT. The divide instruction does not automaticallyset up the RCOUNT value, and it must, therefore, beexplicitly and correctly specified in the REPEAT instruc-tion, as shown in Table 2-1 (REPEAT will execute the tar-get instruction {operand value + 1} times). The REPEATloop count must be set up for 18 iterations of the DIV/DIVF instruction. Thus, a complete divide operationrequires 19 cycles.

TABLE 2-1: DIVIDE INSTRUCTIONS

2.4 DSP Engine

The DSP engine consists of a high-speed 17-bit x17-bit multiplier, a barrel shifter, and a 40-bit adder/sub-tractor (with two target accumulators, round andsaturation logic).

The dsPIC30F devices have a single instruction flowwhich can execute either DSP or MCU instructions.Many of the hardware resources are shared betweenthe DSP and MCU instructions. For example, theinstruction set has both DSP and MCU multiplyinstructions which use the same hardware multiplier.

The DSP engine also has the capability to perform inher-ent accumulator-to-accumulator operations, whichrequire no additional data. These instructions are ADD,SUB and NEG.

The DSP engine has various options selected throughvarious bits in the CPU Core Configuration register(CORCON), as listed below:

1. Fractional or Integer DSP Multiply (IF).2. Signed or Unsigned DSP Multiply (US).3. Conventional or Convergent Rounding (RND).

4. Automatic Saturation On/Off for AccA (SATA).5. Automatic Saturation On/Off for AccB (SATB).6. Automatic Saturation On/Off for Writes to Data

Memory (SATDW).7. Accumulator Saturation mode Selection

(ACCSAT).

A block diagram of the DSP engine is shown inFigure 2-2.

Note: The divide flow is interruptible. However,the user needs to save the context asappropriate.

Instruction Function

DIVF Signed fractional divide: Wm/Wn → W0; Rem → W1

DIV.sd Signed divide: (Wm+1:Wm)/Wn → W0; Rem → W1

DIV.s Signed divide: Wm/Wn → W0; Rem → W1

DIV.ud Unsigned divide: (Wm+1:Wm)/Wn → W0; Rem → W1

DIV.u Unsigned divide: Wm/Wn → W0; Rem → W1

Note: For CORCON layout, see Table 3-3.

TABLE 2-2: DSP INSTRUCTION SUMMARY

Instruction Algebraic Operation

CLR A = 0

ED A = (x – y)2

EDAC A = A + (x – y)2

MAC A = A + (x * y)

MOVSAC No change in A

MPY A = x * y

MPY.N A = – x * y

MSC A = A – x * y

DS70150C-page 16 © 2007 Microchip Technology Inc.

dsPIC30F6010A/6015

FIGURE 2-2: DSP ENGINE BLOCK DIAGRAM

Zero Backfill

Sign-Extend

BarrelShifter

40-bit Accumulator A40-bit Accumulator B

RoundLogic

X D

ata

Bus

To/From W Array

Adder

Saturate

Negate

32

3233

16

16 16

16

4040

40 40

Saturate

Y D

ata

Bus

40

Carry/Borrow Out

Carry/Borrow In

16

40

Multiplier/Scaler17-bit

© 2007 Microchip Technology Inc. DS70150C-page 17

dsPIC30F6010A/6015

2.4.1 MULTIPLIER

The 17x17-bit multiplier is capable of signed orunsigned operations and can multiplex its output usinga scaler to support either 1.31 fractional (Q31) or 32-bitinteger results. Unsigned operands are zero-extendedinto the 17th bit of the multiplier input value. Signedoperands are sign-extended into the 17th bit of the mul-tiplier input value. The output of the 17x17-bit multiplier/scaler is a 33-bit value, which is sign-extended to40 bits. Integer data is inherently represented as asigned two’s complement value, where the MSB isdefined as a sign bit. Generally speaking, the range ofan N-bit two’s complement integer is -2N-1 to 2N-1 – 1.For a 16-bit integer, the data range is -32768 (0x8000)to 32767 (0x7FFF), including 0. For a 32-bit integer, thedata range is -2,147,483,648 (0x8000 0000) to2,147,483,645 (0x7FFF FFFF).

When the multiplier is configured for fractional multipli-cation, the data is represented as a two’s complementfraction, where the MSB is defined as a sign bit and theradix point is implied to lie just after the sign bit(QX format). The range of an N-bit two’s complementfraction with this implied radix point is -1.0 to (1-21-N).For a 16-bit fraction, the Q15 data range is -1.0(0x8000) to 0.999969482 (0x7FFF), including 0 andhas a precision of 3.01518x10-5. In Fractional mode, a16x16 multiply operation generates a 1.31 product,which has a precision of 4.65661x10-10.

The same multiplier is used to support the MCU multi-ply instructions, which include integer 16-bit signed,unsigned and mixed sign multiplies.

The MUL instruction may be directed to use byte orword-sized operands. Byte operands will direct a 16-bitresult, and word operands will direct a 32-bit result tothe specified register(s) in the W array.

2.4.2 DATA ACCUMULATORS AND ADDER/SUBTRACTOR

The data accumulator consists of a 40-bit adder/sub-tractor with automatic sign extension logic. It can selectone of two accumulators (A or B) as its pre-accumulation source and post-accumulation destina-tion. For the ADD and LAC instructions, the data to beaccumulated or loaded can be optionally scaled via thebarrel shifter, prior to accumulation.

2.4.2.1 Adder/Subtractor, Overflow and Saturation

The adder/subtractor is a 40-bit adder with an optionalzero input into one side and either true or complementdata into the other input. In the case of addition, thecarry/borrow input is active-high and the other input istrue data (not complemented), whereas in the case ofsubtraction, the carry/borrow input is active-low and theother input is complemented. The adder/subtractorgenerates Overflow Status bits, SA/SB and OA/OB,which are latched and reflected in the STATUS register.

• Overflow from bit 39: this is a catastrophic overflow in which the sign of the accumulator is destroyed.

• Overflow into guard bits 32 through 39: this is a recoverable overflow. This bit is set whenever all the guard bits are not identical to each other.

The adder has an additional saturation block whichcontrols accumulator data saturation, if selected. Ituses the result of the adder, the Overflow Status bitsdescribed above, and the SATA/B (CORCON<7:6>)and ACCSAT (CORCON<4>) mode control bits todetermine when and to what value to saturate.

Six STATUS register bits have been provided tosupport saturation and overflow. They are:

1. OA:AccA overflowed into guard bits

2. OB: AccB overflowed into guard bits

3. SA:AccA saturated (bit 31 overflow and saturation)orAccA overflowed into guard bits and saturated(bit 39 overflow and saturation)

4. SB:AccB saturated (bit 31 overflow and saturation)orAccB overflowed into guard bits and saturated(bit 39 overflow and saturation)

5. OAB:Logical OR of OA and OB

6. SAB:Logical OR of SA and SB

The OA and OB bits are modified each time data passesthrough the adder/subtractor. When set, they indicatethat the most recent operation has overflowed into theaccumulator guard bits (bits 32 through 39). The OA andOB bits can also optionally generate an arithmetic warn-ing trap when set and the corresponding overflow trapflag enable bit (OVATE, OVBTE) in the INTCON1 regis-ter (refer to Section 5.0 “Interrupts”) is set. This allowsthe user to take immediate action, for example, to correctsystem gain.

DS70150C-page 18 © 2007 Microchip Technology Inc.

dsPIC30F6010A/6015

The SA and SB bits are modified each time data passesthrough the adder/subtractor, but can only be cleared bythe user. When set, they indicate that the accumulatorhas overflowed its maximum range (bit 31 for 32-bitsaturation, or bit 39 for 40-bit saturation) and will besaturated if saturation is enabled. When saturation is notenabled, SA and SB default to bit 39 overflow and thusindicate that a catastrophic overflow has occurred. If theCOVTE bit in the INTCON1 register is set, SA and SBbits will generate an arithmetic warning trap whensaturation is disabled.

The Overflow and Saturation Status bits can optionallybe viewed in the STATUS register (SR) as the logicalOR of OA and OB (in bit OAB) and the logical OR of SAand SB (in bit SAB). This allows programmers to checkone bit in the STATUS register to determine if eitheraccumulator has overflowed, or one bit to determine ifeither accumulator has saturated. This would be usefulfor complex number arithmetic which typically usesboth the accumulators.

The device supports three Saturation and Overflowmodes.

1. Bit 39 Overflow and Saturation:When bit 39 overflow and saturation occurs, thesaturation logic loads the maximally positive 9.31(0x7FFFFFFFFF) or maximally negative 9.31value (0x8000000000) into the target accumula-tor. The SA or SB bit is set and remains set untilcleared by the user. This is referred to as ‘supersaturation’ and provides protection against erro-neous data or unexpected algorithm problems(e.g., gain calculations).

2. Bit 31 Overflow and Saturation:When bit 31 overflow and saturation occurs, thesaturation logic then loads the maximally posi-tive 1.31 value (0x007FFFFFFF) or maximallynegative 1.31 value (0x0080000000) into thetarget accumulator. The SA or SB bit is set andremains set until cleared by the user. When thisSaturation mode is in effect, the guard bits are notused so the OA, OB or OAB bits are never set.

3. Bit 39 Catastrophic OverflowThe bit 39 Overflow Status bit from the adder isused to set the SA or SB bit, which remain setuntil cleared by the user. No saturation operationis performed and the accumulator is allowed tooverflow (destroying its sign). If the COVTE bit inthe INTCON1 register is set, a catastrophicoverflow can initiate a trap exception.

2.4.2.2 Accumulator ‘Write-Back’

The MAC class of instructions (with the exception ofMPY, MPY.N, ED and EDAC) can optionally write arounded version of the high word (bits 31 through 16)of the accumulator that is not targeted by the instructioninto data space memory. The write is performed acrossthe X bus into combined X and Y address space. Thefollowing addressing modes are supported:

1. W13, Register Direct:The rounded contents of the non-targetaccumulator are written into W13 as a 1.15fraction.

2. [W13]+ = 2, Register Indirect with Post-Increment:The rounded contents of the non-target accumu-lator are written into the address pointed to byW13 as a 1.15 fraction. W13 is thenincremented by 2 (for a word write).

2.4.2.3 Round Logic

The round logic is a combinational block, which per-forms a conventional (biased) or convergent (unbiased)round function during an accumulator write (store). TheRound mode is determined by the state of the RND bitin the CORCON register. It generates a 16-bit, 1.15 datavalue which is passed to the data space write saturationlogic. If rounding is not indicated by the instruction, atruncated 1.15 data value is stored and the leastsignificant word is simply discarded.

Conventional rounding takes bit 15 of the accumulator,zero-extends it and adds it to the ACCxH word (bits 16through 31 of the accumulator). If the ACCxL word (bits0 through 15 of the accumulator) is between 0x8000and 0xFFFF (0x8000 included), ACCxH is incre-mented. If ACCxL is between 0x0000 and 0x7FFF,ACCxH is left unchanged. A consequence of this algo-rithm is that over a succession of random roundingoperations, the value will tend to be biased slightlypositive.

Convergent (or unbiased) rounding operates in thesame manner as conventional rounding, except whenACCxL equals 0x8000. If this is the case, the LSb(bit 16 of the accumulator) of ACCxH is examined. If itis ‘1’, ACCxH is incremented. If it is ‘0’, ACCxH is notmodified. Assuming that bit 16 is effectively random innature, this scheme will remove any rounding bias thatmay accumulate.

The SAC and SAC.R instructions store either a trun-cated (SAC) or rounded (SAC.R) version of the contentsof the target accumulator to data memory, via the X bus(subject to data saturation, see Section 2.4.2.4 “DataSpace Write Saturation”). Note that for the MAC classof instructions, the accumulator write-back operationwill function in the same manner, addressing combinedMCU (X and Y) data space though the X bus. For thisclass of instructions, the data is always subject torounding.

© 2007 Microchip Technology Inc. DS70150C-page 19

dsPIC30F6010A/6015

2.4.2.4 Data Space Write Saturation

In addition to adder/subtractor saturation, writes to dataspace may also be saturated, but without affecting thecontents of the source accumulator. The data spacewrite saturation logic block accepts a 16-bit, 1.15fractional value from the round logic block as its input,together with overflow status from the original source(accumulator) and the 16-bit round adder. These arecombined and used to select the appropriate 1.15fractional value as output to write to data spacememory.

If the SATDW bit in the CORCON register is set, data(after rounding or truncation) is tested for overflow andadjusted accordingly. For input data greater than0x007FFF, data written to memory is forced to the max-imum positive 1.15 value, 0x7FFF. For input data lessthan 0xFF8000, data written to memory is forced to themaximum negative 1.15 value, 0x8000. The MSb of thesource (bit 39) is used to determine the sign of theoperand being tested.

If the SATDW bit in the CORCON register is not set, theinput data is always passed through unmodified underall conditions.

2.4.3 BARREL SHIFTER

The barrel shifter is capable of performing up to 16-bitarithmetic or logic right shifts, or up to 16-bit left shiftsin a single cycle. The source can be either of the twoDSP accumulators or the X bus (to support multi-bitshifts of register or memory data).

The shifter requires a signed binary value to determineboth the magnitude (number of bits) and direction of theshift operation. A positive value will shift the operandright. A negative value will shift the operand left. Avalue of ‘0’ will not modify the operand.

The barrel shifter is 40 bits wide, thereby obtaining a40-bit result for DSP shift operations and a 16-bit resultfor MCU shift operations. Data from the X bus is pre-sented to the barrel shifter between bit positions 16 to31 for right shifts, and bit positions 0 to 15 for left shifts.

DS70150C-page 20 © 2007 Microchip Technology Inc.

dsPIC30F6010A/6015

TABLE 3-1: PROGRAM SPACE ADDRESS CONSTRUCTION

FIGURE 3-2: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

Access TypeAccessSpace

Program Space Address<23> <22:16> <15> <14:1> <0>

Instruction Access User 0 PC<22:1> 0

TBLRD/TBLWT User (TBLPAG<7> = 0)

TBLPAG<7:0> Data EA <15:0>

TBLRD/TBLWT Configuration (TBLPAG<7> = 1)

TBLPAG<7:0> Data EA <15:0>

Program Space Visibility User 0 PSVPAG<7:0> Data EA <14:0>

0Program Counter

23 bits

1

PSVPAG Reg

8 bits

EA

15 bits

Program

Using

Select

TBLPAG Reg

8 bits

EA

16 bits

Using

Byte24-bit EA

0

0

1/0

Select

User/Configuration

TableInstruction

ProgramSpace

Counter

Using

Space Select

Note: Program Space Visibility cannot be used to access bits <23:16> of a word in program memory.

Visibility

DS70150C-page 22 © 2007 Microchip Technology Inc.

dsPIC30F6010A/6015

3.1.1 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

This architecture fetches 24-bit wide program memory.Consequently, instructions are always aligned. How-ever, as the architecture is modified Harvard, data canalso be present in program space.

There are two methods by which program space canbe accessed; via special table instructions, or throughthe remapping of a 16K word program space page intothe upper half of data space (see Section 3.1.2 “DataAccess From Program Memory Using ProgramSpace Visibility”). The TBLRDL and TBLWTL instruc-tions offer a direct method of reading or writing the leastsignificant word of any address within program space,without going through data space. The TBLRDH andTBLWTH instructions are the only method whereby theupper 8 bits of a program space word can be accessedas data.

The PC is incremented by two for each successive24-bit program word. This allows program memoryaddresses to directly map to data space addresses.Program memory can thus be regarded as two 16-bitword-wide address spaces, residing side by side, eachwith the same address range. TBLRDL and TBLWTLaccess the space which contains the lsw, and TBLRDHand TBLWTH access the space which contains theMSB.

Figure 3-2 shows how the EA is created for table oper-ations and data space accesses (PSV = 1). Here,P<23:0> refers to a program space word, whereasD<15:0> refers to a data space word.

A set of table instructions are provided to move byte orword-sized data to and from program space.

1. TBLRDL: Table Read LowWord: Read the least significant word of theprogram address;P<15:0> maps to D<15:0>.Byte: Read one of the Least Significant Bytes ofthe program address;P<7:0> maps to the destination byte when byteselect = 0;P<15:8> maps to the destination byte when byteselect = 1.

2. TBLWTL: Table Write Low (refer to Section 6.0“Flash Program Memory” for details on FlashProgramming).

3. TBLRDH: Table Read HighWord: Read the most significant word of theprogram address;P<23:16> maps to D<7:0>; D<15:8> always be = 0.Byte: Read one of the Most Significant Bytes ofthe program address;P<23:16> maps to the destination byte whenbyte select = 0;The destination byte will always be = 0 whenbyte select = 1.

4. TBLWTH: Table Write High (refer to Section 6.0“Flash Program Memory” for details on FlashProgramming).

FIGURE 3-3: PROGRAM DATA TABLE ACCESS (LEAST SIGNIFICANT WORD)

0816PC Address

0x0000000x000002

0x0000040x000006

2300000000

00000000

00000000

00000000

Program Memory‘Phantom’ Byte(Read as ‘0’).

TBLRDL.W

TBLRDL.B (Wn<0> = 1)

TBLRDL.B (Wn<0> = 0)

© 2007 Microchip Technology Inc. DS70150C-page 23

dsPIC30F6010A/6015

FIGURE 3-5: DATA SPACE WINDOW INTO PROGRAM SPACE OPERATION

3.2 Data Address Space

The core has two data spaces. The data spaces can beconsidered either separate (for some DSP instruc-tions), or as one unified linear address range (for MCUinstructions). The data spaces are accessed using twoAddress Generation Units (AGUs) and separate datapaths.

3.2.1 DATA SPACE MEMORY MAP

The data space memory is split into two blocks, X andY data space. A key element of this architecture is thatY space is a subset of X space, and is fully containedwithin X space. In order to provide an apparent LinearAddressing space, X and Y spaces have contiguousaddresses.

When executing any instruction other than one of theMAC class of instructions, the X block consists of the64 Kbyte data address space (including all Yaddresses). When executing one of the MAC class ofinstructions, the X block consists of the 64 Kbyte dataaddress space excluding the Y address block (for datareads only). In other words, all other instructions regardthe entire data memory as one composite addressspace. The MAC class instructions extract the Yaddress space from data space and address it usingEAs sourced from W10 and W11. The remaining X dataspace is addressed using W8 and W9. Both addressspaces are concurrently accessed only with the MACclass instructions.

A data space memory map is shown in Figure 3-6.

Figure 3-7 shows a graphical summary of how X and Ydata spaces are accessed for MCU and DSPinstructions.

23 15 0

PSVPAG(1)15

15

EA<15> = 0

EA<15> = 1

16DataSpace

EA

Data Space Program Space

8

15 23

0x0000

0x8000

0xFFFF

0x00

0x017FFE

Data Read

Upper half of Data Space is mapped into Program Space

Note: PSVPAG is an 8-bit register, containing bits <22:15> of the program space address (i.e., it defines the page in program space to which the upper half of data space is being mapped).

0x001200AddressConcatenation

BSET CORCON,#2 ; PSV bit setMOV #0x00, W0 ; Set PSVPAG registerMOV W0, PSVPAGMOV 0x9200, W0 ; Access program memory location

; using a data space access

0x000100

© 2007 Microchip Technology Inc. DS70150C-page 25

dsPIC30F6010A/6015

FIGURE 3-6: dsPIC30F6010A/6015 DATA SPACE MEMORY MAP

0x0000

0x07FE

0x17FE

0xFFFE

Least Significant ByteAddress16 bits

LSBMSB

Most Significant ByteAddress

0x0001

0x07FF

0x17FF

0xFFFF

0x8001 0x8000

OptionallyMappedinto ProgramMemory

0x27FF 0x27FE

0x28000x2801

0x0801 0x0800

0x1801 0x1800

NearData

0x1FFE0x1FFF

2 KbyteSFR Space

8 Kbyte

SRAM Space

8 Kbyte

Space

Unimplemented (X)X Data

SFR Space

X Data RAM (X)

Y Data RAM (Y)

DS70150C-page 26 © 2007 Microchip Technology Inc.

dsPIC30F6010A/6015

FIGURE 3-7: DATA SPACE FOR MCU AND DSP (MAC CLASS) INSTRUCTIONS EXAMPLE

SFR SPACE

(Y SPACE)

X S

PA

CE

SFR SPACE

UNUSED

X S

PA

CE

X S

PA

CE

Y SPACE

UNUSED

UNUSED

Non-MAC Class Ops (Read/Write) MAC Class Ops Read-Only

Indirect EA using any W Indirect EA using W10, W11 Indirect EA using W8, W9

MAC Class Ops (Write)

© 2007 Microchip Technology Inc. DS70150C-page 27

dsPIC30F6010A/6015

3.2.2 DATA SPACES

The X data space is used by all instructions and sup-ports all addressing modes. There are separate readand write data buses. The X read data bus is the returndata path for all instructions that view data space ascombined X and Y address space. It is also the Xaddress space data path for the dual operand readinstructions (MAC class). The X write data bus is theonly write path to data space for all instructions.

The X data space also supports Modulo Addressing forall instructions, subject to addressing mode restric-tions. Bit-Reversed Addressing is only supported forwrites to X data space.

The Y data space is used in concert with the X dataspace by the MAC class of instructions (CLR, ED,EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to pro-vide two concurrent data read paths. No writes occuracross the Y bus. This class of instructions dedicatestwo W register pointers, W10 and W11, to alwaysaddress Y data space, independent of X data space,whereas W8 and W9 always address X data space.Note that during accumulator write-back, the dataaddress space is considered a combination of X and Ydata spaces, so the write occurs across the X bus.Consequently, the write can be to any address in theentire data space.

The Y data space can only be used for the dataprefetch operation associated with the MAC class ofinstructions. It also supports Modulo Addressing forautomated circular buffers. Of course, all other instruc-tions can access the Y data address space through theX data path, as part of the composite linear space.

The boundary between the X and Y data spaces isdefined as shown in Figure 3-6 and is not user pro-grammable. Should an EA point to data outside its ownassigned address space, or to a location outside phys-ical memory, an all-zero word/byte will be returned. Forexample, although Y address space is visible by allnon-MAC instructions using any addressing mode, anattempt by a MAC instruction to fetch data from thatspace, using W8 or W9 (X space pointers), will return0x0000.

All Effective Addresses are 16 bits wide and point tobytes within the data space. Therefore, the data spaceaddress range is 64 Kbytes or 32K words.

3.2.3 DATA SPACE WIDTH

The core data width is 16 bits. All internal registers areorganized as 16-bit wide words. Data space memory isorganized in byte addressable, 16-bit wide blocks.

3.2.4 DATA ALIGNMENT

To help maintain backward compatibility with PIC®

devices and improve data space memory usage effi-ciency, the dsPIC30F instruction set supports bothword and byte operations. Data is aligned in data mem-ory and registers as words, but all data space EAsresolve to bytes. Data byte reads will read the completeword, which contains the byte, using the LSb of any EAto determine which byte to select. The selected byte isplaced onto the LSB of the X data path (no byteaccesses are possible from the Y data path as the MACclass of instruction can only fetch words). That is, datamemory and registers are organized as two parallelbyte wide entities with shared (word) address decode,but separate write lines. Data byte writes only write tothe corresponding side of the array or register whichmatches the byte address.

As a consequence of this byte accessibility, all EffectiveAddress calculations (including those generated by theDSP operations, which are restricted to word-sizeddata) are internally scaled to step through word-alignedmemory. For example, the core would recognize thatPost-Modified Register Indirect Addressing mode,[Ws++], will result in a value of Ws + 1 for byteoperations and Ws + 2 for word operations.

All word accesses must be aligned to an even address.Misaligned word data fetches are not supported, socare must be taken when mixing byte and word opera-tions, or translating from 8-bit MCU code. Should amisaligned read or write be attempted, an addresserror trap will be generated. If the error occurred on aread, the instruction underway is completed, whereas ifit occurred on a write, the instruction will be executedbut the write will not occur. In either case, a trap willthen be executed, allowing the system and/or user toexamine the machine state prior to execution of theaddress Fault.

FIGURE 3-8: DATA ALIGNMENTTABLE 3-2: EFFECT OF INVALID MEMORY ACCESSES

Attempted Operation Data Returned

EA = an unimplemented address 0x0000

W8 or W9 used to access Y data space in a MAC instruction

0x0000

W10 or W11 used to access X data space in a MAC instruction

0x0000

15 8 7 0

0001

0003

0005

0000

0002

0004

Byte 1 Byte 0

Byte 3 Byte 2

Byte 5 Byte 4

LSBMSB

DS70150C-page 28 © 2007 Microchip Technology Inc.

dsPIC30F6010A/6015

All byte loads into any W register are loaded into theLSB. The MSB is not modified.

A sign-extend (SE) instruction is provided to allowusers to translate 8-bit signed data to 16-bit signedvalues. Alternatively, for 16-bit unsigned data, userscan clear the MSB of any W register by executing azero-extend (ZE) instruction on the appropriateaddress.

Although most instructions are capable of operating onword or byte data sizes, it should be noted that someinstructions, including the DSP instructions, operateonly on words.

3.2.5 NEAR DATA SPACE

An 8 Kbyte ‘near’ data space is reserved in X addressmemory space between 0x0000 and 0x1FFF, which isdirectly addressable via a 13-bit absolute address fieldwithin all memory direct instructions. The remaining Xaddress space and all of the Y address space isaddressable indirectly. Additionally, the whole of X dataspace is addressable using MOV instructions, whichsupport memory direct addressing with a 16-bitaddress field.

3.2.6 SOFTWARE STACK

The dsPIC DSC device contains a software stack. W15is used as the Stack Pointer.

The Stack Pointer always points to the first availablefree word and grows from lower addresses towardshigher addresses. It pre-decrements for stack pops andpost-increments for stack pushes, as shown inFigure 3-9. Note that for a PC push during any CALLinstruction, the MSB of the PC is zero-extended beforethe push, ensuring that the MSB is always clear.

There is a Stack Pointer Limit register (SPLIM) associ-ated with the Stack Pointer. SPLIM is uninitialized atReset. As is the case for the Stack Pointer, SPLIM<0>is forced to ‘0’, because all stack operations must beword-aligned. Whenever an Effective Address (EA) isgenerated using W15 as a source or destinationpointer, the address thus generated is compared withthe value in SPLIM. If the contents of the Stack Pointer(W15) and the SPLIM register are equal and a pushoperation is performed, a stack error trap will not occur.The stack error trap will occur on a subsequent pushoperation. Thus, for example, if it is desirable to causea stack error trap when the stack grows beyondaddress 0x2000 in RAM, initialize the SPLIM with thevalue, 0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap isgenerated when the Stack Pointer address is found tobe less than 0x0800, thus preventing the stack frominterfering with the Special Function Register (SFR)space.

A write to the SPLIM register should not be immediatelyfollowed by an indirect read operation using W15.

FIGURE 3-9: CALL STACK FRAME

3.2.7 DATA RAM PROTECTION FEATURE

The dsPIC30F6010A/6015 devices support Data RAMprotection features which enable segments of RAM tobe protected when used in conjunction with Boot andSecure Code Segment Security. BSRAM (Secure RAMsegment for BS) is accessible only from the Boot Seg-ment Flash code when enabled. SSRAM (Secure RAMsegment for RAM) is accessible only from the SecureSegment Flash code when enabled.

See Table 3-3 for an overview of the BSRAM andSSRAM SFRs.

Note: A PC push during exception processingwill concatenate the SRL register to theMSB of the PC prior to the push.

<Free Word>

PC<15:0>

000000000

015

W15 (before CALL)

W15 (after CALL)

Sta

ck G

row

s To

war

dsH

ighe

r A

ddre

ss

PUSH: [W15++]POP: [--W15]

0x0000

PC<22:16>

© 2007 Microchip Technology Inc. DS70150C-page 29

dsP

IC30F

6010A/6015

DS

70150C-page 30

© 2007 M

icrochip Technology Inc.

Bit 2 Bit 1 Bit 0 Reset State

0000 0000 0000 0000

0000 0000 0000 0000

0000 0000 0000 0000

0000 0000 0000 0000

0000 0000 0000 0000

0000 0000 0000 0000

0000 0000 0000 0000

0000 0000 0000 0000

0000 0000 0000 0000

0000 0000 0000 0000

0000 0000 0000 0000

0000 0000 0000 0000

0000 0000 0000 0000

0000 0000 0000 0000

0000 0000 0000 0000

0000 1000 0000 0000

0000 0000 0000 0000

0000 0000 0000 0000

0000 0000 0000 0000

0000 0000 0000 0000

0000 0000 0000 0000

0000 0000 0000 0000

0000 0000 0000 0000

0000 0000 0000 0000

0000 0000 0000 0000

0000 0000 0000 0000

0000 0000 0000 0000

uuuu uuuu uuuu uuuu

uuuu uuuu uuuu uuuu

0 uuuu uuuu uuuu uuu0

TH 0000 0000 0uuu uuuu

0 uuuu uuuu uuuu uuu0

H 0000 0000 0uuu uuuu

TABLE 3-3: CORE REGISTER MAP

SFR Name Address(Home) Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3

W0 0000 W0 / WREG

W1 0002 W1

W2 0004 W2

W3 0006 W3

W4 0008 W4

W5 000A W5

W6 000C W6

W7 000E W7

W8 0010 W8

W9 0012 W9

W10 0014 W10

W11 0016 W11

W12 0018 W12

W13 001A W13

W14 001C W14

W15 001E W15

SPLIM 0020 SPLIM

ACCAL 0022 ACCAL

ACCAH 0024 ACCAH

ACCAU 0026 Sign Extension (ACCA<39>) ACCAU

ACCBL 0028 ACCBL

ACCBH 002A ACCBH

ACCBU 002C Sign Extension (ACCB<39>) ACCBU

PCL 002E PCL

PCH 0030 — — — — — — — — — PCH

TBLPAG 0032 — — — — — — — — TBLPAG

PSVPAG 0034 — — — — — — — — PSVPAG

RCOUNT 0036 RCOUNT

DCOUNT 0038 DCOUNT

DOSTARTL 003A DOSTARTL

DOSTARTH 003C — — — — — — — — — DOSTAR

DOENDL 003E DOENDL

DOENDH 0040 — — — — — — — — — DOEND

Legend: u = uninitialized bit

Note: Refer to “dsPIC30F Family Reference Manual” (DS70046) for descriptions of register bit fields.

© 2007 M

icrochip Technology Inc.

DS

70150C-page 31

dsP

IC30F

6010A/6015

SR V Z C 0000 0000 0000 0000

CO V RND IF 0000 0000 0010 0000

MO XWM<3:0> 0000 0000 0000 0000

XM 0 uuuu uuuu uuuu uuu0

XM 1 uuuu uuuu uuuu uuu1

YM 0 uuuu uuuu uuuu uuu0

YM 1 uuuu uuuu uuuu uuu1

XB uuuu uuuu uuuu uuuu

DI 0000 0000 0000 0000

BS BSR IR_BSR RL_BSR 0000 0000 0000 0000

SS SSR IR_SSR RL_SSR 0000 0000 0000 0000

TA

SF t 2 Bit 1 Bit 0 Reset State

Le

0042 OA OB SA SB OAB SAB DA DC IPL2 IPL1 IPL0 RA N O

RCON 0044 — — — US EDT DL2 DL1 DL0 SATA SATB SATDW ACCSAT IPL3 PS

DCON 0046 XMODEN YMODEN — — BWM<3:0> YWM<3:0>

ODSRT 0048 XS<15:1>

ODEND 004A XE<15:1>

ODSRT 004C YS<15:1>

ODEND 004E YE<15:1>

REV 0050 BREN XB<14:0>

SICNT 0052 — — DISICNT<13:0>

RAM 0750 — — — — — — — — — — — — — IW_

RAM 0752 — — — — — — — — — — — — — IW_

BLE 3-3: CORE REGISTER MAP (CONTINUED)

R Name Address(Home) Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bi

gend: u = uninitialized bit

Note: Refer to “dsPIC30F Family Reference Manual” (DS70046) for descriptions of register bit fields.

dsPIC30F6010A/6015

4.0 ADDRESS GENERATOR UNITS

The dsPIC DSC core contains two independentAddress Generator Units (AGU): the X AGU and YAGU. The Y AGU supports word-sized data reads forthe DSP MAC class of instructions only. The dsPIC DSCAGUs support three types of data addressing:

• Linear Addressing

• Modulo (Circular) Addressing• Bit-Reversed Addressing

Linear and Modulo Data Addressing modes can beapplied to data space or program space. Bit-ReversedAddressing mode is only applicable to data spaceaddresses.

4.1 Instruction Addressing Modes