Contents Section Page Title & Contents (this page) 1 Notes & Gate Identification 2 Block Diagram 3 Timing 4 Keyboard and Control (part 1) 5 Control (part 2) 6 Control (part 3) 7 Registers 8 Arithmetic 9 Decimal Point Management 10 Display 11 Power Supply 12 Timing Diagram 13 IC Pinouts 14 IC Notes & Gate Construction 15 Connectors 16 Commodore DAC-612 Calculator Commodore DAC-612 Calculator Section: Title and Contents Page: 1 Rendition: 2014 Mar 7 This schematic has been derived through reverse engineering. This is not the manufacturer’s schematic, nor is it based on the manufacturer’s schematic.

Welcome message from author

This document is posted to help you gain knowledge. Please leave a comment to let me know what you think about it! Share it to your friends and learn new things together.

Transcript

Contents Section Page

Title & Contents (this page) 1Notes & Gate Identification 2Block Diagram 3Timing 4Keyboard and Control (part 1) 5Control (part 2) 6Control (part 3) 7Registers 8Arithmetic 9Decimal Point Management 10Display 11Power Supply 12Timing Diagram 13IC Pinouts 14IC Notes & Gate Construction 15Connectors 16

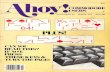

Commodore DAC-612Calculator

Commodore DAC-612 CalculatorSection: Title and Contents

Page: 1 Rendition: 2014 Mar 7

This schematic has been derived through reverse engineering.This is not the manufacturer’s schematic, nor is it based on the manufacturer’s schematic.

Notes

♦ Gate symbols and signal names are presented in accordance with: logic 0 = GND (0V) logic 1 = V–24

♦ A lowercase “n” in a signal name indicates the logical NOT operation.

♦ The symbol Ncpp denotes a physical connector pin where c=connector, and pp=pin. Solid black end is the male side of the connector. White end is the female side of the connector.

♦ connection between different sections. connection limited to same section. Arrows indicate direction of signal or energy flow.

♦ The symbol denotes V–24.

♦ Resistance in ohms unless otherwise indicated.

♦ Capacitance in microfarads unless otherwise indicated.

♦ These drawings based on unit with Serial No. 209040.

♦ SC1772 ICs of Unit 209040 stamped with 6921 and 6945.

♦ Drawn Jan. to Feb. 2000 by bhilpert. See www.cs.ubc.ca/~hilpert/eec for additional information.

Gate Identification

Gates and logic elements are identified by a symbol of the form:b g n

whereb = board (A, B or C)g = gate type identifier (1 or 2 characters, see table below)n = number

andboard A = lower boardboard B = upper boardboard C = display board

See “Connectors” page for more about board identification.

Gate Type ID Description A discrete AND gateO discrete OR gateS 12–bit shift register in µPD11 ICU 2–input OR gate in µPD101C ICV 3–input OR gate in µPD102C ICY 48–bit shift register in SC1772 IC1D 2 or 3–input OR gate in HD3106 IC1E flip-flop in HD3107 IC1L inverter in µPD13C IC1M serial BCD adder in HD3112 IC1R 48–bit shift register in µPD106 IC2C flip–flop in µPD10(C) IC2D 4–input OR gate in µPD15C IC2E switch in µPD110C IC

See “IC Pinouts and Gate Construction” page for more about the integrated circuits.

Commodore DAC-612 CalculatorSection: Notes

Page: 2 Rendition: 2014 Mar 7

V+170

X

N1

KAC, KC,KADD, KSUB, KMUL, KDIV,KGT, KDP,

KOFF, K54,KENTER

V+90V–24

Z Register(accumulator, 48 bits)

Y Register(2nd operand, 48 bits)

X Register(displayed operand, 48 bits)

Arithmetic7-segment Decoder

and Display

Power SupplyTiming

Y

Z

SUM

Commodore DAC-612 CalculatorSection: Block Diagram

Page: 3 Rendition: 2014 Mar 7

Decimal Point Set-pointRing Counter

Ring Counter

Decimal Point DisplayRing Counter

PD

DP

ØC ØT ØBxbit timing

ØDxdigit timing

PS

PT

Display Latch(4 bits)

N2

N4

N8

KNUM

V–14

Control

AL1 AL2

NEG

Keyboard

ØB8•C

12

131

ØT

ØT

ØB8•CC2C3

D Q

ØC

122

4

ØT10 ØT

ØB8•CC2C3

D Q

ØC

113

ØT

ØD2

ØT

ØB8•CC2C3

D Q

ØC

95

ØD3

ØT

ØB8•CC2C3

D Q

ØC

86

ØD4

ØT

ØB8•CC2C2

D Q

ØC

122

4

ØT 10

ØD5

ØT

ØB8•CC2C2

D Q

ØC

113

ØT

ØD6

ØT

ØB8•CC2C2

D Q

ØC

95

ØT

ØD7

ØT

C2C2

D Q

ØC

86

ØT

ØD8

ØT

C2C1

D Q

ØC

122

4

ØT 10

ØD9

ØT

ØB8•CC2C1

D Q

ØC

113

ØT

ØD10

ØT

ØB8•CC2C1

D Q

ØC

95

ØT

ØT

ØB8•CC2C1

D Q

ØC

86

410C1L1

2.2K

C73522K

5.6K

C735

22K

100

22K

10K3.3

25VINIT

NA23NC8

nINIT

NB3 Na39

ØCNB27 Na285.6K

BN3A495

5.6K

4.7K330pF

2.2K

BN4A495

5.6K

22K

nINIT

ØD11

NC15 NA17

NB14

ØD12

NB16

NA12 NC13

NB15 NC14

NA19

ØB8•C

NC23

ØT

ØCB2C1

D Q

ØC

113

ØT ØT

ØCB2C1

D Q

ØC

95

ØT ØT

ØCB2C1

D Q

ØC

86

Nb20 NA30ØB4

410B1L3

NB31 NC4ØnB8

ØB8

ØB2

ØB1

NB29 NC12

1

2 3BU2BA5

ØB8

ØC

2

Commodore DAC-612 CalculatorSection: Timing

Page: 4 Rendition: 2014 Mar 7

BV1

CA2

AA64ØnD12

ØB8•C

ØnD12•B8•C

Nb16 Na35ØD12•B8•C

10K

BE1C735

5

4 6BU2BA3

ØB8•C

ØD12

ØT

ØB8•CA1E1

D Q

ØC

1314

ØT

5

6 7A1D1

ØD12

INIT

AA25ØD12

ØCØD12•C

NB38 NA4

NC22

311C1L1

ØD0

NC6 NB25

NA28

NC19 Nb8

NA9

68C1L1

ØD1

NC7 NB23

NA31

ØnD1

NC21

NA6

AE1C735

1

1 1

M 1

1

1

1 1 1

1

1

ØB8•C

212C1L1

NC20 NB6

Na38

1

ØnD12 ØnD0

1

13

13

AA37ØnD12

ØCØnD12•C

1

10K

5.6K220pF5.6K 220pF

5.6K

BN2A495

5.6K

4.7K330pFBPC735

BGC735

82K82K

2.2K

BN1A495

5.6K

22K

BE2C735

10K

BE3C735

10K

C735

10K

C735

10K

NN

N N N N N N N N N

ØT

ØT ØT

ØT

Nb3

SXLN (RX1)

AO2KGT

AA46KENTER 2

AA42SR2

SR1 2

SL4 (S6)10K

AE2C735

AA41SnR2

SR1 2

AA612 3

11A1L5 M

13

12 11AU11

113A1L5M

SnL6 (S4,A1)

SL6 (S2)

143

2

A1D1M

INITKAC

6

345

AV2M

SnR2

12

12

13AV2

MKC

212A1L2

SL1 (PD1)

SnL1 (RX2,PD1)M

AA582KENTER

SR2AA29

1ØCØnD12

SMARKEDSR11

AA552

68A1L31

SnL5 (A1,PD1)

SL5 (S1,A2,RX1,PD2)Na21 Nb31

1

2 3AU3M 2

12A1L5M

SnL2 (S6,A1,RY1)Na20 Nb23

4

5 6AU3M

SL3 (S2)AA60

2KMATH

KMATH

KGT

1

2 3BU1MKDP

12

12A1L3

12

11 13B2E2M

2BA4

Nb35 NA32

SnL6

SZCLR (RZ1)

AA402KC

SL4

SnL6

NA33 NB22KC

SnL2

2AA56

KENTER

SL4

Na23 Nb37

1

2 3B2E2M

5

4 6B2E2M

Nb39 Na34

SL8 (PD1)

13

12 11BU5M

SR13SL27 (S1)

SR5

SL12

SL7 (S1,RX2)

AL2

GT

0

1

×

3

4

5

6

7

8

9

0

1

2

3

4

5

6

7

8

9

+=

–=

2

÷

DP

AC NK20

C

NA36

NK25 Na19

NK23 Na25

NK17 Na31

NK6 Na33

NK19 Na29

NK21 Na27

NK27 NB18

NK1 Nb42

NK2

NK3

NK4

NK14

NK9

NK11

NK13

NK8

NK15

Na9

Nb40

Nb38

Nb36

Nb34

Nb32

Nb30

Nb28

Nb26

Nb24

NB21

Commodore DAC-612 CalculatorSection: Keyboard and Control (part 1)

Page: 5 Rendition: 2014 Mar 7

470K

ØB2

470K

470K

ØB4

ØB8

B2D1

2345

1

ØB1

BA9

BA8

BA7

0

KNUM (RX1)

KAC (S1,PS1)

KC (S3)

KGT (S3)

KSUB (A1)

KDIV (S1)

KDP (S2)

K54 (A1)

5.6K

BA102

OFF5/4CUT

NK12

NK5 Na3KOFF (R1,PS1)

BO1Nb18

KENTER (S4,PS1)NA21

BO4

13579

BO3

2367

BO2

4567

8

9

AO5

AO4

AO6

KAS (S4)

KMD (S4)

KMATH (S3)

5.6K

5.6K

5.6K

5.6K

5.6K

5.6K

5.6K

5.6K

5.6K

AU4

ØT

ØD12•B8•CA2C1

D Q

ØC

122

ØT

410A1L5

ØT

ØD12•B8•CA2C1

D Q

ØC

113

ØT

311A1L3

4

10

MM

M

1

SR1 (S2)

SR2 (S3)

SnR1 (S1)

Na8 Nb25SnR2 (S4,A1)

2

1 3M

AA432

AA442

AO3KGTKDP

KENTERKMATH

Commodore DAC-612 CalculatorSection: Control (part 2)

Page: 6 Rendition: 2014 Mar 7

ØT

ØD12•B8•CA2C1

D Q

ØC

95

ØT2

12

ØT

ØD12•B8•CA2C1

D Q

ØC

86

ØT

B1L3

M

M

M

NA10 NB39SR3 (S1,RY1,PS1)

NA14 NB30SR8 (A1,RX1)

Nb13 Na11SnR3 (S2)

ØT

ØD12•B8•CB2C2

D Q

ØC

122

ØT

ØT

ØD12•B8•CB2C2

D Q

ØC

113

ØT

ØT

ØD12•B8•CB2C2

D Q

ØC

95

ØT

311ØT

ØD12•B8•CB2C2

D Q

ØC

86

ØTA1L2

4

10

M

M

M

M

1

SR4 (DS2)

SRND54 (A1,RX1,RY1)

NB32 NA38

SR7 (S2,A1)

SR5 (S4,A2)

SnR5 (DS1,DT1)

Nb7 NA13

ØT

ØD12•B8•CB2C3

D Q

ØC

122

ØT

ØT

ØD12•B8•CB2C3

D Q

ØC

113

ØT

ØT

ØD12•B8•CB2C3

D Q

ØC

95

ØT

ØT

ØD12•B8•CB2C3

D Q

ØC

86

ØT

4

10

M

M

M

M

SR10 (S2,A1)

SR11 (S3,A1)NB41 Na41

SR12 (S3)

SR9 (DT1)

ØT

ØD12•B8•CB2C4

D Q

ØC

122

ØT

ØT

ØD12•B8•CB2C4

D Q

ØC

113

ØT

ØT

ØD12•B8•CB2C4

D Q

ØC

95

ØT

ØT

ØD12•B8•CB2C4

D Q

ØC

86

ØT

4

10

M

M

M

M

SR13 (S4,R1)

SR16 (S2,A2)

SR14 (S2,A5)

SR15 (S1,A1)

Nb6 NA26

SnL2

12

2131

BV4 MSL24

BA22AL1 2

BA23AnL1

2

410A1L3

5

4 6AU11

1

AA452

SL9

BA36SL17

2

BA312

ØT

ØD12•B8•C A1E1

D Q

ØC

43

ØT

1

A1E1

D Q

ØC

56

ØT

2

7

1 Na18 Nb10

KMD

AA36SL3

1

13

12 11AU4M

AA632SL13

KDIV

10

SL13

KAS

1

2 3B2E4M5

4 6B2E4M

BA32SL12

2

SR5

PL1

1

2 3BU4M

2BA38

SnMARKSnL17

12

13 11BU4M

2BA37SMARK

SnL17

BA21SR13

2

2

1 3BU5M

MBA20SnL2

311B1L2

SL12

M9

10 8BU5SL17

PT

SnL2 M10

9 8BU4

SL10 (A1)

5

4 6BU3M

2BA33

SR12

AA512

KAS

SL4SL6

NA37 Nb11SnL9

SL3

M6

8B1L2

68A1L5

SL9 (S3)M

9 8AU4M

SnL9 (S3)

BA42SL16

2SL11 (S1)

SL16

SL19

AA471

N1N8

ØB8•CØD11

AA53

AA548

10119

AV2M

M

M

ØnD1

SDONEG (A1)

SL5

SL20

SnL2

4

5 6AU4M

SnL2

SL13 (S3,RY1)Na15 NB36

AA592

KMD

SnR1SnL6

AA482

KAS

SnL6SL4

SnR3 212A1L11

SnL22 (RX1,RY1)

SL22 (A1)Na2 NB37

12

13 11BU2M

SZLOAD (A1,RZ1)NB11 Na40BA12

2SR3

SR7

AA492 Na1 Nb1

1

2 3BU3

SL4

KMD10

9 8AU31

AA62

KAS

KMD

AA522

SL4Na5 Nb12SL6

NA8Nb2MSL15 (RY1,DT1)

BA21

ØD12SR5

SnL17

ØC

6

543

BV1BA142

SL17SL27

M

SnR21

13B1L2

212B1L2M

SL12 (S5)

SnL12 (S5,A1)

ØD0

BA172ØC

SMARKSR14

11

12 13B2E5MX

9

8 10B2E5M

PD

BA39

BA40

6

543

BV4M

2

2

SnL12

BA412ØD12•B8•C

SR13

SL13

SnR2

ØT

AS4

D Q12

ØC

27

ØT9

8

M

5

6 4A2E1

8

9 10A2E1M

M

M

3

2 1A2E3

M

ØnD0

Nb4NA22SnMARK (S1)

68A1L2

ØnD12•B8•C

MAA50

ØD1

3 4MSR2

8

91011

BV4M

SL11NA29Nb15SR10

Nb17NA11SMARK (S2)

13

12 11A2E2

12

11 13A2E1

ØC

M

MSMARKED (S1,RY1)

1AA15ØnD0

ØD12

5

4 6BU51BA44

SL12

SR13

2BA43

SR16

M

5

4 6BU4M

SR10 NB5 Na26

Nb19 NA7

SL26 (S1,A2,RY2)

SL25 (PS1)

2BA11

SR7

SnR3

NB35 NA35SL20 (S1,A1,RX1)

B2D1

9121110

13MSR14

SR15SR11

SL21 (A1,RY1)

2BA15

SL12

SR5 Nb33 Na30SL18 (RX2,PD1)

2BA19

SnL12

SR16

NB42 NA42SL19 (S1,RY1,DT1)

M9

10 8BU3SR12

SnL9

12

13 11BU3M

SL14 (A2,RX1,PD1)Nb9 NA16

SR12

SnL9

SL9

SL9SL16 (S2)

SL24

SL24 (S2)

11

12 13B2E3

9

8 10B2E3ØD1

M

M

8119

10

BV31

BA18N8

ØC

BA26SR11

ØD12

M

1212

13

BV3

ØD11

2

SnL17 (S3)

SL17 (S3,A1,R1)

SL26SL7

Commodore DAC-612 CalculatorSection: Control (part 3)

Page: 7 Rendition: 2014 Mar 7

Commodore DAC-612 CalculatorSection: Registers

Page: 8 Rendition: 2014 Mar 7

Nb41

Na42

A2D2

109

1112

13AA11

AA9SUM

68A1L4

BA6KNUM

ØD0ØT

AY1

D Q48

ØC

110

ØT8

7

12

213

1AV1

ØnD12•C

A2D2432

5

1AA12

SUM

68A1L1

410A1L1

ØT

A1R1

D Q48

ØC

94

ØT7

3

Y (A1)

311A1L1

AA8X

SL15

AA101

13A1L2

SnL2 AA13

ØT

AY2

D Q48

ØC

110

ØT8

7

Z (A1)

2

3 1A2E4

113A1L3

2

3 1A2E1

AA14SUM

13

12 11AU2

ØnD12•C 10

9 8AU2

AA26ØD12•C

SUMNb29Na13

X (A1,S1)

AA33

SnL22

SnL22

AA28ØD12•C

SnL1

SnL1

SZCLR

SZLOAD

SXLN

KOFF

ØnD12•C 4

5 6AU2

AA27ØD12•C

ØD12•C

8

10119

BV1SR8 Na24NB20SL7

B2D2

2345

1

SRND54SL20SL14SL5

113B1L3

BA13SRND54

SR3

6

543

BV2NB7 Na22

SL13

SMARKED

SL19

SL21SL26

SL18

AA34SL18

ØD0

AA38

11

13

12SL7 A2E4

8

10

9 A2E4SL26

XYL1 (P1)BA34SL17

SR13 NB40 Na36

M

M

M

M

3

3

1

1

1

1

1

1

1

2

2

11

1

M

M

M

1

3

M

M

1

M

M

2

NC16NB12

N2 (A1,D1)

NB13NC17

68C1L2

NC9NB19N4 (A1,D1)

NA39

NC3NB26

NA41

Commodore DAC-612 CalculatorSection: Arithmetic

Page: 9 Rendition: 2014 Mar 7

ØT

ØC

B1M1

Serial BCD Adder

nA

nQ1

ØC

11

8

ØT

nQ2 14

nQ4 16

nQ8 18

8

9 10B2E1

113B1L1

4

5 6B2E1

N1 (S1,A1,D1)

N8 (S2,A1,D1)10

24

12

1

2 3B2E1ØD12

Øn(DE•B8)

ØnB8 ØnB820

19

5

4 6BU1N1

9

10 8BU1N4

311B1L1

68B1L1nSUM 15

410B1L1

Na32NB28

NC2SUM (RX2,RY1,RZ1)

ØD0BA25

?13

?21BA24

BA1ØC

ØD0

SR14

SR16

nB7

ØB11

2 3B2E5

410A1L4

311A1L4AA24 NB4

Na7

Y

Z

ØD0ØB8•C

SR5

Na16NB10

B2D2

1012

911

13

212B1L1

9

10 8BU2

ØnD12

Na10NB9

ØnD12

11

12 13B2E4ØnD0

BA30

M

M

1

1

1

2

M

M

1

M

M

M

M

M

M

M

M

M

1

2

M

M

M

M

M

11

12 13B2E1ØnD12 M

4

5 6B2E3

M

2

1 3B2E3

5

4 6B2E6

8

9 10B2E6

M(NS)

M

68B1L3

nSUB98

9 10B2E2MØD0

SR8

6

345

BV3SR16

MSR10

BA27SnL12

SR5 2

8

91011

BV2SL26SL14

SR14

nsSL17

SR14 2

ØB1

4

5 6B2E5M

8

9 10B2E4

ØnD0

ØnD12

SR15

SR11

M

SRND54

11

12 13B2E6

2

1 3B2E6M

MM

BA28

BA29M

N2

N8

ØB1ØD0

SR7

SR14

K54

? 174

10B1L2

AL1 (S1)M

MAnL1 (S1)

SZLOAD

SL22

BA16SR14

ØD0 M

12

13 11BU1MKSUB

BA352

SnR2

SL21

SL10

SL5

NB17Na17212A1L4AA35

XØnD12

113A1L4

1

12

12

13BV2

SL26

MSL14

Na14NB8SL5

1

2 3AU21

ØT

ØCB2C1

D Q

ØC

122

ØT

M3

4

10Na37

Nb22

AL2 (S1)

AA57SnL6

11

10 9A1D1M

SnL5

2

1 NC1NA40NEG (D1)

SDONEG NB34NA20

SnL2 AA39

311B1L3M

SL20

M

NC5NB24

Commodore DAC-612 CalculatorSection: Decimal Point Management

Page: 10 Rendition: 2014 Mar 7

A2D1

9121011

13AA18

PS

ØT

AS1

D Q12

ØC

27

ØT9

8

113A1L1

AA20PT

9

10 8AU1

AA31ØD12

MM

AA171

AA19ØD0

2

2

2

AA32

2

ØnD12

1

ØT

ØB8•CA1E1

D Q

ØC

1211

ØT

1 1

Nb14

NA15 NC18DP (PS1,D1)

ØT

AS3

D Q12

ØC

27

ØT9

8

M5

6 4A2E3

9

10 8A2E3

AA4DP

M

1

ØnD12•B8•C

M

12

13 11AU3M

ØT

AS2

D Q12

ØC

27

ØT9

8

M5

6 4A2E2

2

1 3A2E2

AA3PD

M

M

ØnD12•B8•C

M

8

9 10A2E21

M

1

10

ØnD1

8

91110

AV1

ØnD12•B8•C

6

5 4A2E4M

M

ØnD1

3 4M

3 4M

3 4M

Nb21NA3PT (PD1,S1)

NA18PS (PD1,PT1)

Nb27NA5PD (PT2,S1)

SL15

16

131214

A1D1M

INITAA1

KAC 2

SnR5

AO1KOFF

KENTERAA16

2

SR4

AA22

SR4

SnL1

SL1

AA222

ØC

AA232

PD

6

345

AV1

PS

SR3

M

410A1L2

ØB4ØnD12•C

A2D1

5342

1

AA6MØB4

ØnD12•C

AA7M

AA5SL25

M

SR9

AA301

AA211

SL8

ØD12•B8•C

SnL5

SL5

SnR5

12

11 13A2E31ØB1

ØnD0

Nb5NA24PL1 (S1)

SL19

1ØD12•B8•C

2

1 3AU1SL5

SL18

SL14

XYL1

CN20A617

DIGIT 12 (MSD)V+170

56K

V+90

— (negative)

CN4C284

12K

56K

NEG

DIGITS 11 to 1 (LSD)

Digit Transistor11 CN1110 CN129 CN228 CN167 CN136 CN175 CN154 CN143 CN212 CN181 CN19

V+90

5.6K

1

n1

ØD12

12K

3.3K22K

a

d c

fe

b

g p

RODANELFIN

MG–17D

56K

V+90

15K56K

CN3C284

12K

56K

V+90

15K56K

CN6C284

12K

56K

V+90

15K56K

CN8C284

12K

56K

V+90

15K56K

CN5C284

12K

56K

V+90

15K56K

CN9C284

12K

56K

V+90

15K56K

CN7C284

12K

56K

V+90

15K56K

CN1C735

12K

33K

22K

56K

CN10C284

ØT

ØB8•CC2C4

D Q

ØC

122

ØT 113C1L2

2

n2ØT

ØB8•CC2C4

D Q

ØC

113

ØT 212

4

n4ØT

ØB8•CC2C4

D Q

ØC

95

ØT 311

n8

N8

ØT

ØB8•CC2C4

D Q

ØC

86

ØT 410

C1L2

C1L2

C1L2

CN2C284

2.2K

56K

33K

V+90

33K1

13C1L1ØnB8

ØB8

16

1

n1n2

6

5 7

10

11 9

CA4

n1

n4

n2n8

n4

n8

121413

C1D124

n1

1

1

234

2n4

n1

4

1

24

1

C1D1

4

n2

1

N4

N2

N1

DP

4

10

abcdefgp

Commodore DAC-612 CalculatorSection: Display

Page: 11 Rendition: 2014 Mar 7

C1D1

CA9

CA13

CA6

CA12

CA3

CA7

CA8

CA5

CA10

CA11 C1D1

CA1

1

1

1

1

1

1

1

1

1

1

1

1

560

470

680

POWER

5.6K

28VAC

?

3900.5W

100K

V–14

75VAC

black

22160V

22160V

47050V

2SD91

C970

MZ1012

V+170

V+90

0.047

1 AMP. 220V117V100V

240V

red100K

yellow

brown

ZH110

10025V

NA1,2

NB1,2

NC24

NA43,44

NC10

NB43,44

Na43,44

Nb43,44

NK7

V–24

brown

brown

violet

violet

bSn

µPD11

5

10

b1Ln

µPD13C

b2Dn

µPD15C

14

77

black

blue

grey

NC27

NC25

Commodore DAC-612 CalculatorSection: Power Supply

Page: 12 Rendition: 2014 Mar 7

bUn

µPD101C

14

7

bVn

µPD102C

14

7

b1Rn

µPD106

5

10

b2En

µPD110C

7

b1Dn

HD31060D

15

8

b1En

HD31070C

15

8

b2Cn

µPD10C

14

7

bYn

SC1772

6

5

3

B1M1

HD31120D

23

12

22

V–14

3

2

8

1

AS1AS2AS3AS4

A1L1A1L2A1L3A1L4A1L5

B1L1B1L2B1L3

C1L1C1L2

A2D1A2D2

B2D1B2D2

AU1AU2AU3AU4

BU1BU2BU3BU4BU5

AV1AV2

BV1BV2BV3BV4

A1R1 A2E1A2E2A2E3A2E4

B2E1B2E2B2E3B2E4B2E5B2E6

A1D1

C1D1

A1E1A2C1

B2C1B2C2B2C3B2C4

C2C1C2C2C2C3C2C4

AY1AY2

B1M1

28VAC

0µS 901080

Commodore DAC-612 CalculatorSection: Timing Diagram

Page: 13 Rendition: 2014 Mar 7

(44 KHz) ØC

ØT

(11 KHz) ØB1

ØB2

ØB4

ØB8

ØB8•C

(847 Hz) ØD0

ØD1

ØD12

1 1

ØnD12•C

PD

180 270 360 450 540 630 720 810 900 990 108011700µS 90

2 3 4 5 6 7 8 9 10 11 12 1 1

XX and PD with

000987654321.in the display.

One full number cyclein registers

Digit being displayed,also ØDn

Digit in register outputs

1(LSD)

2 3 4 5 6 7 8 9 10 11 12(MSD)

-12 -

logic 1 (V–24)

logic 0 (GND)

ØD12•C

ØnD12•B8•C

ØD12•B8•C

NECµPD10C

id: 2C

–24V

GND

14 13 12 11 10 9 8

1 2 3 4 5 6 7

NECµPD11

id: S

NECµPD13C

id: 1L

GND

14 13 12 11 10 9 8

1 2 3 4 5 6 7

NECµPD15C

id: 2D

14 13 12 11 10 9 8

1 2 3 4 5 6 7

NECµPD101C

id: U

14 13 12 11 10 9 8

1 2 3 4 5 6 7

NECµPD102C

id: V

14 13 12 11 10 9 8

1 2 3 4 5 6 7

NECµPD106

id: 1R

NECµPD110C

id: 2E

14 13 12 11 10 9 8

1 2 3 4 5 6 7

–24V

HITACHIHD3106 0D

id: 1D

HITACHIHD3107 0C

id: 1E

PHILCOSC1772

id: Y

GND

16 15 14 13 12 11 10

1 2 3 4 5 6 7

9

8

16 15 14 13 12 11 10

1 2 3 4 5 6 7

9

8

HITACHIHD3112 0B

id: 1M

24 23 22 21 20 19 18

1 2 3 4 5 6 7

17

8

16 15 14

9 10 11

13

12

- 7 8 9 10 11 12

6 - 5 4 3 2 1

10 9 8 7 6

1 2 3 4 5

10 9 8 7 6

1 2 3 4 5

10 9 8 7 6

1 2 3 4 5

–24V

GND

µPD10:

µPD10:

–24V

GND

–14V

–24V

GND GND

–24V

GND

GND

–24V

GND

GND GND

GND

–24V

GND

–24V

GND

GND

–24V

Commodore DAC-612 CalculatorSection: IC Pinouts

Page: 14 Rendition: 2014 Mar 7

Q48

D ØT ØC48–bit shift register

DØC48–bit shift register

ØTQ48

ØT

ØC –24V Q1Q8A NEGB

?Q2Q4 SUM?ØD12•B8

Q8ØB8?

D QDØCØT

Q12

Q4

Q DØCØTØTØC

D Q Q DØCØTØTØC

Serial BCD Adder

?

12–bit shift register

Q

DØC

ØTQ

DØC

ØTQ

DØC

ØTQ

DØC

ØT

Notes on Integrated Circuits

♦ Based on supply voltage, circuit impedances and logic density, IC technology are presumed to be early MOS.

♦ Outputs are open-collector, except SC1772.

♦ These diagrams presented in accordance with:• Logic FALSE or 0 is considered to be GND.• Logic TRUE or 1 is considered to be –24V.

♦ Some ICs in the µPD family came in two packages: TO-100/101 cans and 14-pin DIPs. The C suffix indicates the DIP package.

♦ Inferred for µPD110C:The 4 elements are not standard logic elements. They appear to be MOS transistors. They function as a bidirectional switch, or as a 2–input OR gate with one input inverted.

switch is closed when logicalcontrol input b is TRUE (–24V) equivalent

Care is taken in the logic design to ensure another “wire-ANDed” output does not feed back through the element to affect the state of the signal driving the non-inverted input.

♦ Inferred for flip-flops:The flip-flops in this logic family appear to be Master/Slave D-type flip-flops with the clocks for the master and slave sections kept separate. This permits a system design where data capture is done in accordance with the requirements of the logic while all outputs are changed synchronously by a single clock signal.

ØC = Capture Input (master section clock) ØT = Toggle Input (slave section clock)

The state of the D input is captured when ØC is TRUE (–24V).The Q output is set in accordance with the captured state when ØT goes TRUE.

♦ Inferred for HD3112:This device appears to be a full-blown Serial BCD Adder, performing serial addition, bit carry, tens carry, correction for digit sums greater than 9, negation, etc.

Commodore DAC-612 CalculatorSection: IC Notes and Gate Construction

Page: 15 Rendition: 2014 Mar 7

a a

b

aa

b

Discrete Gate Construction

Most AND gates are constructed from discrete diodes and resistors. Most OR gates and complex logic elements are contained in integrated circuits. The internal construction of discrete gates is shown in the following diagrams. A wire-AND or wire-OR construction is indicated by the input line traversing the width of the gate.

All gate outputs ,except the few discrete OR gates and the Philco SC1772 shift registers, require external load resistors (R) connected from the output to V–24. To reduce clutter these resistors are indicated in the schematic by one of the following symbols near the output.

Discrete Modular 30K

100K220K

All discrete OR gates are loaded by a 5.6K resistor to ground.

R

bAn

R

5.6K

bOn

12

3M

r r

N

A B CGND 1 2 GND GND 1 2 GND V+170 27

PT 3 4 ØB1 ØT 3 4 a7 26 –PD 5 6 ØnD1 SL26 5 6 ØnD12 V+90 25

SL25 7 8 SL15 a22 7 8 a14 24 GNDØnD0 9 10 SR3 a10 9 10 a16 ØT 23

SMARK 11 12 ØD12 SZLOAD 11 12 N1 22 (ØB1)SR4 13 14 SR8 N4 13 14 ØD11 ØnD1 21

DP 15 16 SL14 ØB8c 15 16 ØD12 20 ØnD12ØD11 17 18 (PS) a17 17 18 KDP ØnD0 19

ØB8•C 19 20 B34 nN4 19 20 a24 18 DPKENTER 21 22 SnMARK KSUB 21 22 A33 N4 17

INIT 23 24 PL1 ØD1 23 24 N2 16 N1– 25 26 SR9 ØD0 25 26 N8 ØD11 15– 27 28 ØD0 Ø C 27 28 SUM 14 ØB8•C

b15 29 30 ØB4 ØB8 29 30 SR8 ØD12 13ØD1 31 32 SL8 ØnB8 31 32 SR5 12 ØB8B22 33 34 – – 33 34 A20 – 11

SL20 35 36 KAC SL20 35 36 SL13 10 V–24 Kb11 37 38 SR5 SL22 37 38 ØB1 nN4 9 KDP 27N1 39 40 NEG SR3 39 40 XYL1 8 INIT 26 –N8 41 42 SL19 SR11 41 42 SL19 ØD1 7 KC 25

V–14 43 44 V–14 V–14 43 44 V–14 6 ØD0 24 –a b N2 5 KGT 23

b1 1 2 SL22 a1 1 2 SL15 4 ØnB8 22 –KOFF 3 4 – K54 3 4 SnMARK N8 3 KDIV 21SL16 5 6 – PL1 5 6 SR9 2 (SUM) 20 KAC

B4 7 8 SnR2 SR4 7 8 ØnD0 NEG 1 KMUL 19KDP 9 10 B9 SL14 9 10 a18 18 –

SnR3 11 12 – A37 11 12 SL16 KADD 17X 13 14 B8 SnR3 13 14 (DP) 16 –

SL13 15 16 B10 A29 15 16 ØD12•B8•C K9 15B17 17 18 b10 SMARK 17 18 KENTER 14 K4KC 19 20 SnL2 SL25 19 20 ØB4 K7 13

SL5 21 22 B7 PT 21 22 a37 12 K54SXLN 23 24 B20 SnL2 23 24 K9 K6 11

KGT 25 26 SL26 SnR2 25 26 K8 10 –KDIV 27 28 Ø C PD 27 28 K7 K5 9

KMUL 29 30 SL18 X 29 30 K6 8 K8KADD 31 32 SUM SL5 31 32 K5 V–24 7KSUB 33 34 SL7 SL18 33 34 K4 6 KSUB

ØD12•B8•C 35 36 XYL1 SL8 35 36 K3 KOFF 5b22 37 38 ØnD12 SXLN 37 38 K2 4 K3ØT 39 40 SZLOAD SL7 39 40 K1 K2 3

SR11 41 42 b41 a42 41 42 K0 2 K1V–24 43 44 V–24 V–24 43 44 V–24 K0 1

Notes:♦ Italicised expressions are connections with no signal name in the schematic.♦ Bold-faced expressions are signal sources.

Commodore DAC-612 CalculatorSection: Connectors

Page: 16 Rendition: 2014 Mar 7

Component Side

NB2

NB1 NB43

NB44 Nb2

Nb1 Nb43

Nb44

Board B (upper board)

Component Side

NA2

NA1 NA43

NA44 Na2

Na1 Na43

Na44

Board A (lower board)

12H-21 B

12H-21 A

board identifiers,note “A” and “B”

Related Documents