Logic Synthesis for Reconfigurable Transistors Akash Kumar Shubham Rai, Michael Raitza Chair for Processor Design

Welcome message from author

This document is posted to help you gain knowledge. Please leave a comment to let me know what you think about it! Share it to your friends and learn new things together.

Transcript

Logic Synthesis for Reconfigurable Transistors

Akash KumarShubham Rai, Michael Raitza

Chair for Processor Design

© Akash Kumar

Where does the reconfigurability come from?

Designing novel combinational gates

How does it benefit us?

Going beyond logic synthesis

Where are we going from here?

What will we learn today?3

© Akash Kumar

Dual-Gate RFETs based Inverter6

A

Vdd

Vss

CMOS Based Inverter

Out

A

P

P

Out

Pull-up

Pull-down

VSS

Pull-up

Pull-down

VDD

VDD

VSS

© Akash Kumar

Multi Input Gate RFETs: NAND7

Vdd

Vss

A B

B

A

CMOS

#of Transistors =4 #of Transistors =3

SiNW with TIGFET

VSS VSS

VDD

VDD

VSS

TIGFET

VDD

VSSSiNW with Dual Gate RFET

B

VDD

VDD

VSS

VDD

VSS

VSS

#of Transistors =4

© Akash Kumar

Reconfigurable Gate8

NAND Gate

P=VSS P=VSS

P=VDD

P=VDD

P=VSSDepending upon value of P,NAND can be configured as NOR

P=VDD P=VDD

P=VSS

P=VSS

P=VDDNOR Gate

© Akash Kumar

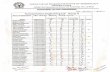

SiNW RFETs vs CMOS12

SiNW RFET

CMOS

No. ofTransistors

44 %

SiNW RFET

CMOS Delay*

25 %

*Using logical effort theory

© Akash Kumar

Extrinsic Reconfigurability Change some bits in the control

path Extra circuitry req. here

13

Extrinsic Reconfigurability

© Akash Kumar

14

Intrinsic Reconfigurability

Intrinsic reconfigurability Unique electrical propertiesfrom the material No extra circuitry.

= 0

NAND

= 1

NOR

= 3rd Input

MINORITY

© Akash Kumar

Design Flow 15

CMOS based logic gateIn

puts

SiNW based logic gate In

puts

A Single Function

Range offunctionsto choose from

CMOS/SiNWGenlib

© Akash Kumar

Area savings over CMOS – post logic synthesis16

0.00 5.00 10.00 15.00 20.00 25.00 30.00 35.00 40.00 45.00

C432

C1355

C1908

C2670

C3540

C6288

C7552

t481

rot

b9

dalu

des

k2

Savings over CMOS

Average = 18%

© Akash Kumar

Design Flow: Adding place and route17

CMOS based logic gateIn

puts

SiNW based logic gate In

puts

A Single Function

Range offunctionsto choose from

CMOS/SiNWGenlib

CMOS/ SiNWLEF File

© Akash Kumar

21

1. Exploring design space of new standard cells, exploiting reconfiguration

a. By using meta-models that represent a multitude of possible circuit topologies

b. Enumeration of all distinct Boolean formulae that can be implemented with a specific meta-model

2. Quantifying found cells using probabilistic transistor modelsa. Approach is agnostic to a specific technologyb. New switching functions / characteristics can be easily addedc. (Probabilistic) delay and activity are possible targets

Other Ongoing Works – Property Checking

© Akash Kumar

24

Use the program gate to camouflage circuits

Only a particular key to activate the circuit Length of the key can be used as a tunable knob

Other keys may to be used to de-activate (kill-switch) the chip

Camouflaging also makes it hard to reverse-engineer a circuit

Other Ongoing Works – Security

© Akash Kumar

25

Important to re-visit logic synthesis for emerging technologies

Exploit ambi-polarity of transistors to make smaller (faster?) circuits

Need to consider post P&R results for a true evaluation

Need better/realistic models of emerging devices

Conclusions

Related Documents