03/21/22 445_23 1 Pipelining ECE-445 Computer Organization Dr. Ron Hayne Electrical and Computer Engineering

7/2/2015445_23 1 Pipelining ECE-445 Computer Organization Dr. Ron Hayne Electrical and Computer Engineering.

Dec 21, 2015

Welcome message from author

This document is posted to help you gain knowledge. Please leave a comment to let me know what you think about it! Share it to your friends and learn new things together.

Transcript

04/19/23 445_23 1

Pipelining

ECE-445

Computer Organization

Dr. Ron Hayne

Electrical and Computer Engineering

04/19/23 445_23 2

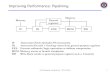

Pipelining

F1 E1

I1

F2 E2

I2

F3 E3

I3

Sequential Execution

F1 E1I1

F2 E2I2

F3 E3I3

Pipelined Execution

04/19/23 445_23 3

Hardware Organization

InstructionFetchUnit

ExecutionUnit

Interstage BufferB1

04/19/23 445_23 4

Four State Pipeline

Fetch (F) Read the instruction from memory

Decode (D) Decode the instruction and fetch the source operand(s)

Execute (E) Perform the operation specified by the instruction

Write (W) Store the result in the destination location

04/19/23 445_23 5

Four Stage Pipeline

04/19/23 445_23 6

Hardware Organization

04/19/23 445_23 7

Data Hazard

Pipeline stalled Source or destination operands not available at time

expected in the pipeline Execution operation taking more than one clock

cycle

04/19/23 445_23 8

Data Hazard

04/19/23 445_23 9

Data Dependency

04/19/23 445_23 10

Operand Forwarding

04/19/23 445_23 11

Operand Forwarding

04/19/23 445_23 12

Handling Data Hazards in SW

Compiler detect data dependencies and deal with them Insert NOPs Attempt to reorder instructions to perform useful tasks in

NOP slots

Side effects Instruction changes contents of a register other than the

named destination Autoincrement/autodecrement addressing modes Condition code flags

Give rise to multiple dependencies Should be minimized

04/19/23 445_23 13

Instruction Hazards

Pipeline stalled Delay in the availability of an instruction

Cache miss Branch instructions

04/19/23 445_23 14

Instruction Hazard

04/19/23 445_23 15

Instruction Queue and Prefetch

04/19/23 445_23 16

Branch Penalty

04/19/23 445_23 17

Branch Prediction

Attempt to predict whether or not a particular branch will be taken

Speculative execution Continue to execute until outcome of branch evaluated No processor registers or memory can be updated until

branch outcome is confirmed

04/19/23 445_23 18

Branch Prediction

Static Branch Prediction Some branch instructions predicted as taken and others

as not taken End or program loop Beginning of program loop Hardware or compiler

Dynamic Branch Prediction Based on execution history

04/19/23 445_23 19

Structural Hazard

Two instructions require use of a given hardware resource at the same time Access to memory

Separate instruction and data caches Access to register file

Multiple port register file

In general avoided by providing sufficient hardware resources on the processor chip

04/19/23 445_23 20

Structural Hazard

04/19/23 445_23 21

Summary

Pipelining does not result in individual instructions being executed faster

Throughput increases Rate at which instruction execution is completed

Important goal in designing processors is to identify all hazards that may cause the pipeline to stall Find ways to minimize their impact

04/19/23 445_23 22

Questions?

Related Documents