DATAPATH SUBSYSTEMS : MULTIPLICATION SUBMITTED BY : SUBMITTED TO: Saurav Shekhar (EC 94) Ravitesh Mishra Swati Soni (EC 109) AP Vijeta Nair (EC 113) EC Dept. Sachin Rajak (EC 84) Roshan Singh (EC 80) Slide 1 Multiplication 04/04/2013

Datapath subsystem multiplication

Jun 19, 2015

THIS PPT IS PRESENTED TO PROF. RAVITESH MISHRA FROM EC FINAL YEAR STUDENTS MADE FROM RAZAVI,DESIGN OF ANALOG CMOS INTEGRATED CIRCUITS ON DATAPATH SUBSYSTEM-MULTIPLICATION

Welcome message from author

This document is posted to help you gain knowledge. Please leave a comment to let me know what you think about it! Share it to your friends and learn new things together.

Transcript

DATAPATH SUBSYSTEMS : MULTIPLICATION

SUBMITTED BY : SUBMITTED TO:

Saurav Shekhar (EC 94) Ravitesh Mishra

Swati Soni (EC 109) AP

Vijeta Nair (EC 113) EC Dept.

Sachin Rajak (EC 84)

Roshan Singh (EC 80)

Slide 1Multiplication 04/04/2013

CONTENT Introduction Data path Operators Multiplications Unsigned Array Multiplication 2’s Complement Array Multiplication Wallace Tree Multiplication Serial Multiplication

MULTIPLICATION Slide 2

INTRODUCTION

Data path elements include adders, multipliers, shifters, BFUs, etc.

– The speed of these elements often dominates the overall system performance so optimization techniques are important.

– However, as we will see, the task is non-trivial since there are multiple equivalent logic and circuit topologies to choose from, each with adv./ disadv. in terms of speed, power and area.

– Also, optimizations focused at one design level, e.g., sizing transistors, leads to inferior designs.

Datapath Slide 3

DATA PATH OPERATORS

It forms an important subclass of VLSI circuit. This arises because n-bit data generally processed, which naturally leads to the ability to use n identical circuits to implement the function. Also, data operations may be sequenced in time or space to each other. Data may be arranged to flow in one direction why any control signals are introduced in an orthogonal direction to the dataflow.

Common Data Path Operators are:

Adders, One/Zero Detectors, Comparators, Counters, Boolean Logic Units, Error-Correcting Code Blocks, Shifters, MULTIPLIERS and Dividers

Datapath Slide 4

MULTIPLICATION

Multiplication is a less common operation than addition but is still essential for microprocessors, digital signal processors and graphics engines. Multiplications algorithm is used to illustrate methods of designing different cells so that they fit into larger structures. The most common form of multiplication consists of forming the product of two unsigned (positive) binary numbers. This can be achieved through the traditional technique taught in primary school, simplified to base 2.

For Example, the multiplication of two positive 4-bit binary integers 12 to base 10 and 5 to base 10 is given below:-

Multiplication Slide 5

Multiplication Slide 6

MULTIPLICATION Example: 1100 : 1210

0101 : 510 1100

Multiplication Slide 7

MULTIPLICATION Example: 1100 : 1210

0101 : 510 1100 0000

Multiplication Slide 8

MULTIPLICATION Example: 1100 : 1210

0101 : 510 1100 0000 1100

Multiplication Slide 9

MULTIPLICATION Example: 1100 : 1210

0101 : 510 1100 0000 1100 0000

Multiplication Slide 10

MULTIPLICATION Example: 1100 : 1210

0101 : 510 1100 0000 1100 000000111100 : 6010

Multiplication Slide 11

MULTIPLICATION Example:

M x N-bit multiplication

– Produce N M-bit partial products.

– Sum these to produce M+N-bit products.

1100 : 1210 0101 : 510 1100 0000 1100 000000111100 : 6010

multiplier

multiplicand

partialproducts

product

Multiplication Slide 12

DOT DIAGRAM Each Dot Represents A Bit

UNSIGNED ARRAY MULTIPLIER

To multiply two 4-bit unsigned array number A3 A2 A1 A0

and B3 B2 B1 B0

The basic block of array is Full Adder Block (FA) and total number of FA block is required is 4 X 3 = 12. The Full Adder block generates output as :-

SUM = CO =

Array Multiplier

Slide 13

C

ACC ...

In general for an n-bit unsigned array multiplier the number of

full adder required is nx(n-1). Each AiBj realized using “AND”

gate. Each output bit is computed by adding the appropriate

AiBjin the respective column and carries from previous column.

To get the final 8-bit output P7 P6 . . . P2 P1 P0 we have to wait

for the maximum combinatorial delay of sum generation of two

FA blocks (row of A3B0) plus carry propagation time of 4 FA

blocks of last and last but one column. Thus it is a fast

multiplier but hardware complexity is also high.

Array Multiplier Slide 14

Multiplication Slide 15

GENERAL FORM Multiplicand: Y = (yM-1, yM-2, …, y1, y0)

Multiplier: X = (xN-1, xN-2, …, x1, x0)

Product:

1 1 1 1

0 0 0 0

2 2 2M N N M

j i i jj i i j

j i i j

P y x x y

PARTIAL PRODUCTS

Multiplication Slide 16

Array Multiplication Slide 17

ARRAY MULTIPLIER

2’s COMPLEMENT ARRAY MULTIPLICATION

Multiplication of 2’s complement numbers are seem more difficult because some partial products are negative and must be subtracted. We know that the most significant bit of a 2’s complement number has a negative weight. Hence, the product is given by :-

2’s COMPLEMENT ARRAY MULTIPLICATION Slide 18

The equation shows that, two of the partial products have negative weight, hence should be subtracted rather than added. The Baugh-Wooley multiplier algorithm handles subtraction by taking the 2’s Complement of terms to be subtracted (i.e. inverting the bits and adding 1). The figure in the next slide shows the partial product that must be summed. The upper parallelogram represents the unsigned multiplication of all but the most significant bits of the inputs. The next roe is single bit corresponding to the product of the most significant bits. The next two pairs of rows are the inversions of the term to subtracted. Each term has implicit leading and trailing 0’s – which are inverted to leading and trailing 1’s. Extra 1’s must be added in the least significant column when taking the 2’s complement.

2’s COMPLEMENT ARRAY MULTIPLICATION Slide 19

2’s COMPLEMENT ARRAY MULTIPLICATION Slide 20

The multiplier delay depends on the number of partial

products rows to be summed. The modified Baugh-Wooley

multiplier reduces this number of partial products by pre

computing the sums of constant 1’s and pushing some of the

terms upwards into extra columns. The figure in next slide

shows such arrangement.

2’s COMPLEMENT ARRAY MULTIPLICATION Slide 21

2’s COMPLEMENT ARRAY MULTIPLICATION Slide 22

2’s COMPLEMENT ARRAY MULTIPLICATION Slide 23

2’s COMPLEMENT GENERATOR

2’s COMPLEMENT ARRAY MULTIPLICATION Slide 24

WALLACE TREE MULTIPLICATION Slide 25

WALLACE TREE MULTIPLICATION

A Carry Save Adder (CSA) is effectively a 1’s counter that adds the number of 1’s on the input and encodes them on the sum carry outputs.

Therefore a CSA is also known as a (3,2) counter, because it converts three input into a count encoded in two outputs.

The carry out is passed to the next most significant column. And this process is go on and on.

The output is produced in carry-save redundant form suitable for the final CPA.

An Adder as a 1’s Counter

A B C CARRY SUM Number of 1’s

0 0 0 0 0 0

0 0 1 0 1 1

0 1 0 0 1 1

0 1 1 1 0 2

1 0 0 0 1 1

1 0 1 1 0 2

1 1 0 1 0 2

1 1 1 1 1 3

WALLACE TREE MULTIPLICATION Slide 26

WALLACE TREE MULTIPLICATION Slide 27

The column addition is slow because only one CSA is active at a time. Another way to speed the column addition is to sum partial products in parallel rather than sequentially. The figure in the next slide shows a Wallace Tree using this approach. The Wallace Tree requires :-

log3/2

levels of (3,2) counters to reduce N input down to 2 carry-save redundant from outputs.

WALLACE TREE MULTIPLICATION Slide 28

2

N

WALLACE TREE MULTIPLICATION Slide 29

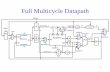

SERIAL MULTIPLICATION

A serial multiplier multiplies 2 input numbers in synchronism with clock. One method of serial multiplication is by repeated addition. Multiplication of two binary numbers A and B is done by repeated addition of B+B+B+…..+B upto A times. Implementation of serial multiplier by repeated addition to multiply two 4-bit unsigned binary number A3 A2 A1 A0 and B3 B2 B1 B0 .

Serial Multiplication Slide 30

The basic building blocks used are :-

1) ADDER (ADD8) to add two 8-bit numbers.

2) 4-bit Binary Up Counter.

1) COMPARATOR (COM4) which compares two 4-bit binary numbers and output is high if two numbers are same.

2) Data Register (FD8CE) which consists 8 D Flip-Flop to store 8-bit data.

Serial Multiplication Slide 31

The 8-bit data structure is used for internal arithmetic and it avoids the chances of overflow. Zero Padding is done in upper 4-bits of B and 8-bit input is fed one input of adder block. The output of the Adder is fed to the input of the Date Register. The output of Data Register is fed to the other input of the adder block. The Date Register and Counter used have a Clock Enable (CE) and Asynchronous Clear Input (CLR).

Serial Multiplication Slide 32

Serial Multiplication Slide 33

ADVANTAGES Array multipliers may be pipelined to decrease clock

period at the expense of latency. Partial product generation and accumulation are merged,

which makes calculation easy.

Multiplication Slide 34

THANK YOU

Multiplication Slide 35

Multiplication Slide 36

Related Documents