Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx Data Conversion based on FPGA

Data Conversion Based on FPGA Thomas Klein

Oct 30, 2014

Welcome message from author

This document is posted to help you gain knowledge. Please leave a comment to let me know what you think about it! Share it to your friends and learn new things together.

Transcript

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

Data Conversion based on FPGA

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

Agenda

Page 2

Xilinx Introduction & Business Update (20 Minutes)

Xilinx Product Update: 7 Series FPGAs & ZYNQ (25 Minutes)

Break (15 Minutes)

Xilinx High-Speed Interfaces (90 Minutes)

Data Conversion based on FPGA (90 Minutes)

– Xilinx 7 Series FPGAs (technical)

• Clocking

• SelectIO

– Interfacing High-Speed DAC/ADC (TI,NXP) to Xilinx FPGAs (LVDS/DDR,

LVCMOS and JESD204A)

• FMC150 DAC/ADC Daughter Card Overview

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

Example for Real Time DSP Data Aquistion

An FPGA is used for the Converter Interfacing and for Glue Logic.

All subsystem data is passed to and from the DSP processor

through the FPGA. This allows for maximum flexibility, including preprocessing

of the data in front of the DSP.

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

Analog-to-Digital Converters (ADCs) are used to convert analog

signals into digital representations that can be communicated and

processed using digital logic. As demand for data has increased,

higher bandwidth ADCs have become necessary to meet the system

performance requirements. High-performance ADCs can be found in

many applications, including:

– Wireless base station receivers

– Power amplifier linearization

– Multi-carrier, multi-mode receivers

– High interface sampling receivers

– Radar systems

– Test and measurement equipment

– Medical equipment

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

Traditionale Digital Interface Options

Parallel CMOS (3.3V logic)

– Pro: Simple to interface to; lower power at slow Fclk

– Con: Requires lots of IO

– Con: Large, fast output edges can create “spurs” on board if you are not

careful.

LVDS (ANSI/TIA/EIA-644), parallel and serial

– Pro: Support higher data rates

– Pro: Reduce SSO (Simultaneous Switching Outputs) challenges

– Con: More advanced interface connection

– LVDS Features:

• DDR clocks data bits on both, rising and falling edges

• Minimize Number of IOs

• Interleaving: multiple channels interleaved onto one bus

• Serialization: multiple data bits serialized onto fewer number of data lines

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

Increasing System Requirements

High Channel Counts

– Typically 1 channel = 1 ADC

• E.g. 256 channel ultrasound system = 256 12-bit 80Msps ADCs

– Result is increased levels of integration for data converters

• Monolithic 8, and more recently, 16 ADCs are available

• Thus 16 ADCs in 64 pin TQFP

Interface Complexity

– For example, Medical Imaging typically required high speed ADCs

• E.g., 12-bit 80Msps ADC ~ 1Gbps

• 256 ADCs = 256Gbps

– Result is a move to serial interfacing

• Serial LVDS is already common but limited to ~1Gbps

• New standards like JESD204 coming….see later

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

Medical Imaging

Ultrasound Example

Up to 256 ADC Channels

ADCs typically interface to FPGAs or beamformer ASICs

(ADI device shown)

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

What about power?

Increased Integration and Serial Interfacing does help…

– Power saved by integrating the key analog front end components into

a single IC (i.e. Integrated amplification and filtering, etc.)

– Serial LVDS versus parallel bus reduces power

• LVDS offers lower power by using low voltage differential signaling

(~1.5mW per pair), and by significantly reducing I/O count

• Additional benefits of LVDS:

Improved signal integrity

Low system noise

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

FPGA – Data Converter IO

Ultrasound

Ultrasound Example – 64 channels

FPGA

(Virtex-6 LX130T)

Digital I/O (8 x Serial LVDS)

8x Analog

(Differential)

2W

ADI AD9272

(Octal 12-bit

80MSPS ADC)

16

21x CLK

8x RX Data

2

2

2

2

2

2

2

2

ADI AD9272

(Octal 12-bit

80MSPS ADC)

16

21x CLK

8x RX Data

2

2

2

2

2

2

2

2

8x Analog

(Differential)

#1

#8

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

I/O Power Saving

Discrete

ADCs

Parallel

LVDS

Octal

ADCs*

Serial

LVDS

Current 64 x

80mA

64 x 12 x

4mA

64 x

80mA

64 x

4mA

Power 9W 5.5W 9W 0.5W

Based on 64 ADCs 12-bits 80Msps and serial LVDS

*Includes LNA and VGA

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

Analog Interface Problem: I/O Count

More than 1,536 I/O required for AFE interface on 128 channel Medical

Ultrasound System!

– with 10 bit single-ended parallel DACs and serial LVDS ADCs

SOLUTION: JESD204A Serial Interface

– 3.125Gbps per lane

– Multiple synchronized lanes per link

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

XAPP876 – Virtex-5 FPGA Interface to a

JESD204A Compliant ADC

XAPP876 with Reference

Design for Virtex-5

– Reference Design ported to

Virtex-6 already

– Being used by Xilinx Lead

Customers for Product

Development

JESD204B IP Core for 7 Series

FPGAs planed for Q3CY11

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

NXP ADC JESD204A Evaluation Board

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

Next Step: JESD204B

Xilinx taking a leading role in the development of JESD204B

– 15 companies have expressed interest in developing the JESD204B standard

– Xilinx, NXP, ADI, TI, Linear Tech, Maxim, National Semi, Samplify, Altera, Lattice, …

– JESD204B IP planned for 7 Series FPGA devices with transceivers

Four new options have been proposed:

– Increase in upper frequency to 6.25 Gbps

– Use of harmonic multiple of frame clock

– Re-specification of SYNC signal timing

– PHY layer electrical equalization (pre-emphasis)

ASICs on older process nodes will have trouble supporting the higher

performance levels of JESD204B

– FPGAs can support this, thus provide a path to

• High performance, 20 to 50% lower power, Smaller board space, possible lower system cost

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

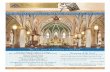

FMC150 DAC/ADC Daughter Card Overview

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

New Virtex-6 FPGA DSP Kit

19

Virtex-6 DSP Development Kit (with ADC/DAC FMC)– Part Number: AES-V6DSP-LX240T-G

– Price: $3,995

– ML605 Board with Virtex-6 LX240T

– Integrated 4DSP FMC150 ADC/DAC Daughter Card:• DAC: Dual-Channel 16-bit, 800 MSPS

• ADC: Dual-Channel, 14-bit, 250 MSPS

– ISE Design Suite: System Edition

– DSP Reference Designs (with AXI4)• Simulink / System Generator

• RTL

• DAC/ADC Integrations

Launch Dates– CEV Testing: Nov 3rd

– Order Entry Open: Nov 12th

– Reference Designs on-line: Nov 12th

– FCS: Dec 6th

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

Adding DAC/ADC to existing kits and boards

Page 20

4DSP FMC150 TI TSW4200EVM

• Single FMC card

• DAC is a dual-channel 16-bit 800 MSPS

high speed data converter with 8-byte

wide DDR LVDS data input.

• The ADC is a dual channel, 14-bit 250

MSPS analog to digital converter.

• Supports data converter configuration

from the FPGA

• Available from 4DSP for $1995

• Planned DSP Kit upgrade

• 4 Card EVM bundle

• DAC is a dual-channel 16-bit 800 MSPS

high speed data converter with 8-byte

wide DDR LVDS data input.

• The ADC is a dual channel, 14-bit 250

MSPS analog to digital converter.

• Supports data converter configuration

from PC workstation

• Available from Avnet for $1295

• Planned DSP Kit upgrade

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

ADC / DAC FMC Cards on xilinx.com

http://www.xilinx.com/products/boards_kits/fmc.htm

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

Xilinx Virtex-6 DSP Kit

Integrated FMC150 ADC/DAC Card from 4DSP

Page 22

4DSP FMC150 Card Details

– 800 MSPS, dual channel, DAC

– 250 MSPS, dual channel, ADC

– TI CDCE72010 clock

synchronizer / jitter cleaner

– Includes on-board clock

generation or external clock

– Can be configured by the FPGA

for:

• Sampling frequency

• Analog input gain

• Offset correction

FMC150 Block Diagram

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

ADS62P49 ADC Overview

Page 23

Applications:

– Wireless communications

infrastructure:

• Remote radio head

• Software-defined radio

• MIMO and diversity receivers

• DPD Feedback

• Communication test and

instrumentation

• Satellite modems

– Radar and advanced imaging

– Man-pack radios

– Portable test equipment

– General-purpose data acquisition

– High-definition video

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

ADS62P49 Digital Interface Timing

Page 24

ADC forwards source-synchronous clock with interleaved DDR data

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

ADS62P49 to FPGA Interface

Page 25

BUFR receives source-synchronous clock forwarded by ADC

BUFR can drive fast regional clock nets AND fabric

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

TI DAC3283 Block Diagram

Page 26

Double-Data Rate (DDR) clocking data on both edges of the clock

Interleaving supports several channels while ensuring that clock

frequencies are in the LVDS I/O range (1.4 Gbps for Virtex-6)

Applications: Cellular Base Stations

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

DAC3283 Digital Interface Timing

Page 27

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

Virtex-6 to DAC3283 Interface

Page 28

Versatile OSERDES can implement various DAC interfaces

DAC3283 contains an internal FIFO to cross clock domains

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

XAPP1071 – Connecting Virtex-6 FPGAs to ADCs with Serial LVDS

Interfaces and DACs with Parallel LVDS Interfaces

Page 30

Recommended Reading:

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

Appendix

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

Data Acquisition DAQ

While each data acquisition system has unique functionality to serve application- specific requirements, all systems

share common components that include signals, sensors, signal conditioning, DAQ hardware, and a computer with

software

Signals/Sensors

A sensor (or transducer) is a device that converts a physical phenomenon into a measurable electrical signal, such as voltage or

current. The following table shows a short list of some common phenomena and the transducers used to measure them.

Phenomenon Transducer

Temperature Thermocouple, RTD, Thermistor

Light Photo Sensor

Sound Microphone

Force and Pressure Strain Gage, Piezoelectric Transducer

Position and Displacement Potentiometer, LVDT, Optical Encoder

Acceleration Accelerometer

pH pH Electrode

Xilinx Confidential – Internal • Unpublished Work © Copyright 2009 Xilinx

Data Acquisition DAQ

Signal Conditioning

Sometimes transducers generate signals too difficult or too dangerous to measure directly with a data acquisition device. For

instance, when dealing with high voltages, noisy environments, extreme high and low signals, or simultaneous signal measurement,

signal conditioning is essential for an effective data acquisition system. It maximizes the accuracy of a system, allows sensors to

operate properly, and guarantees safety.

DAQ Hardware

Data acquisition hardware acts as the interface between a computer and signals from the outside world. It primarily functions as a

device that digitizes incoming analog signals so that the computer can interpret them.

Connection to Signals

Data acquisitions devices typically consist of one or more of the following functions for measuring different types of signals:

Analog inputs – measure analog signals

Analog outputs – generate analog signals

Digital inputs/outputs – measure and generate digital signals

Counter/timers – count events or generate pulses

Multifunction data acquisition boards combine analog, digital, and counter operations on a single device. Additionally, some data

acquisition boards include integrated signal conditioning specific to a signal or sensor type.

Connection to Computer

Data acquisition hardware is offered on several different PC busses. Each bus offers different levels of ease-of-use and performance

and are better suited for different applications.

Computer/Software

Unlike traditional instruments, a computer is a required component in a data acquisition system. Because of this, a user can take

advantage of the ever-increasing performance of the computer’s processor, hard drive, and display for taking measurements,

visualizing data, performing analysis, and storing data.

Related Documents